- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA FFT

Solved!05-29-2023 08:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

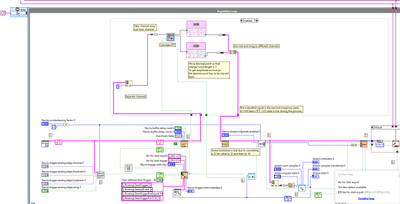

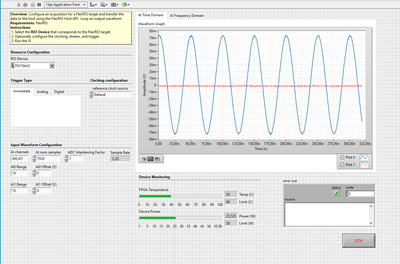

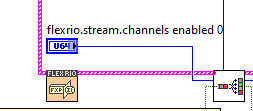

I have a PXIe-5774 digitizer module running my fpga code that is a bit modified version of the getting started default personality code that can be found in example finder (Hardware input and output -> FlexRIO -> Integrated IO -> Getting Started). The part of the block-diagram that I have modified looks like this:

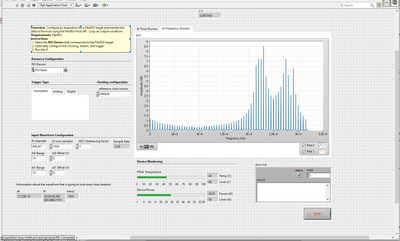

Basically I am trying to calculate an FFT from the CH0 data and send the real and imaginary parts separately to the host. At the host side I am using the basic.vi VI that can be found on the same example but I change the resolution dt (or df) on the waveforms to the correct value and calculate the norm from the real and imaginary parts. When I run this and input 20 MHz frequency to the fpga from my signal generator the result looks like this :

What am I doing wrong because I should be getting a spike on the 20 MHz frequency and not multiple spikes 50 MHz apart? The waveform is the same but the position of the different spikes changes when new results come in each stream. The blockdiagram on the basic.vi (the part I modified) looks like this:

The spikes are the same distant apart if I change the signal generator frequency to like 10 MHz.

I'm very new to this kind of signal processing and fpga stuff. Thanks for your help:

Aarni

Solved! Go to Solution.

- Tags:

- FFT

05-29-2023 10:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, Aarni.

I'm not familiar with handling very high frequency signals, but I wonder if this isn't a problem of "Signal Analysis 101". You are analyzing a signal where the "expected signal" is on the order of 20 MHz, and are acquiring 12-bit (= fairly coarse sampling steps) data at 3 GHz (well over the 10-fold sampling frequency to get rid of aliasing). I suspect that the very first peak of your "spectrum" corresponds to the "signal", and all the rest is some form of generated "noise". This, however, is well out of my "area of expertise" (I deal with signals in the kHz range, in the bio-signal range).

What is the signal? What frequencies do you expect to be in the signal? Is it possible that there could be energy up to 3 GHz there? You are sampling (I'm rounding, here) 1000 points at 3 GHz, so your FFT should consist of 500 gain/phase estimates in steps of 3 MHz from 0 to 1.5 GHz, so all of the "meaningful" data is in that initial peak near the origin (but it doesn't look like it is at 20 MHz ...). Something seems very wrong, here.

Can I suggest that you write a little demo code in "Host" LabVIEW (i.e. that runs on the PC). Simulate a 12-bit A/D converter running at 3.2 GHz that delivers 1024 points of a 20 MHz 1V sinusoid. Use the Host's FFT routines to create a spectrum, and see how it compares to what you have with the FPGA. If it looks similar, then you need to look into "anti-aliasing" filters, or other more advanced signal-processing techniques that are above my level of expertise ...

Bob Schor

05-29-2023 11:03 AM - edited 05-29-2023 12:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

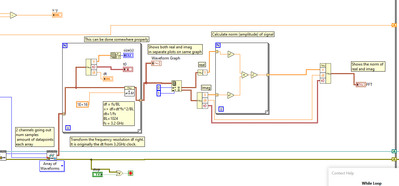

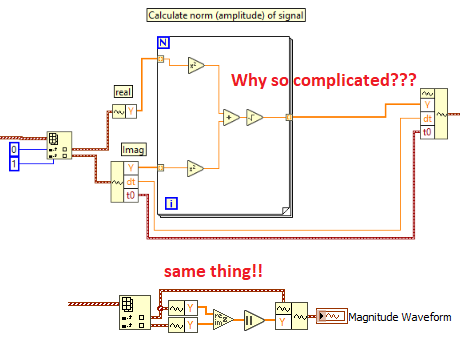

Sorry, I am also not familiar with the FPGA version, but most of your code looks overly complicated.

Just the way you create the magnitude data out of the RE and IM channels boggles the mind. Have a look at the following instead:

(waveform components that are retained don't need to be extraceted/merged, indices don't need to be wired if you want the elements in order, the absolute value of a complex number IS the magnitude, You have a vestigial FOR loop that can be removed without change in outcome, etc.)

From the spectrum you show, it definitely looks like spectral leakage, assuming you expect a few sharp frequencies, so we need to find out if the problem is in the FPGA FFT or in insufficient data.

Can you modify the FPGA code to return the raw waveform section (1024 points?) used to do the FFT and attach it here?

05-29-2023 11:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

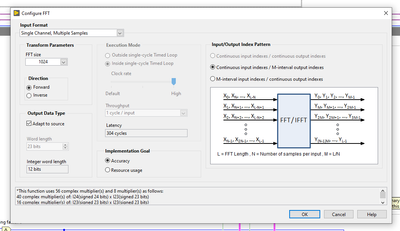

Hello, the LabVIEW FFT function on FPGA (so called WDP FFT: wide data path FFT) requires data reordering for its output. It is kind of a trade-off for its capability to handle multiple samples per clock.

Please refer to a below section of this page (https://www.ni.com/docs/en-US/bundle/labview-fpga-module/page/lvfpga/fpga_fft.html).

"Selecting the Appropriate Input/Output Index Pattern (Single Channel, Multiple Samples Input Format)"

The above explanation can be refered also from dialog panel which opens up when you double-click on Express VI of the FFT function on FPGA.

Another good reference for WDP FFT is an example code located below.

NI Example Finder >> Hardware Input and Output >> FlexRIO >> FPGA Fundamentals >> FFT >> FFT (1 Channle, N samples).lvproj

AI of PXIe-5774 is handled 16 samples per clock at 200MHz so that FPGA can process 3.2GSps. I assume you ran out of most of FPGA resources only with the FFT block (you may be using the one with KU060?) What is the highest bandwidth for your measurement? If it is not required to observe high frequencies such as 1.6GSps, you may first decimate input data from 3.2GSps down to 1.6GSps, or 800MSps, so that the data path to FPGA gets narrower from 16 samples to 8 or 4. Then, apply WDP FFT. This way, you can save up FPGA resource almost by the same factor of your decimation.

Another concern is the data rate from FPGA to host. Based on your block diagram, data rate from FFT to onboard DRAM is 12.8GB/sec during an active sampling. I can not tell how many number of samples you acquire per acquisition cycle, but you cannot transfer this amount of data continuously from FPGA to PC through DRAM. Therefore, you first acquire data for a finite number of samples such as multiple of 4,096 samples. Then, FFT function does 4,096 long FFT and send it to host PC through DRAM.

You may consider to decrease the amount of data by half by sending only half of FFT output, because it looks like FFT does real FFT which yields mirror image. You can dispose half of the results.

Anyway, it is not an easy thing to implement FFT on PXIe-577x series of deivces. It requires at least an year experience of full-time LabVIEW FPGA programming if you learn by yourself. Did NI sales representative give you any information about difficulties of doing this kind of thing? Did they recommend any systems integrator for you?

05-30-2023 12:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

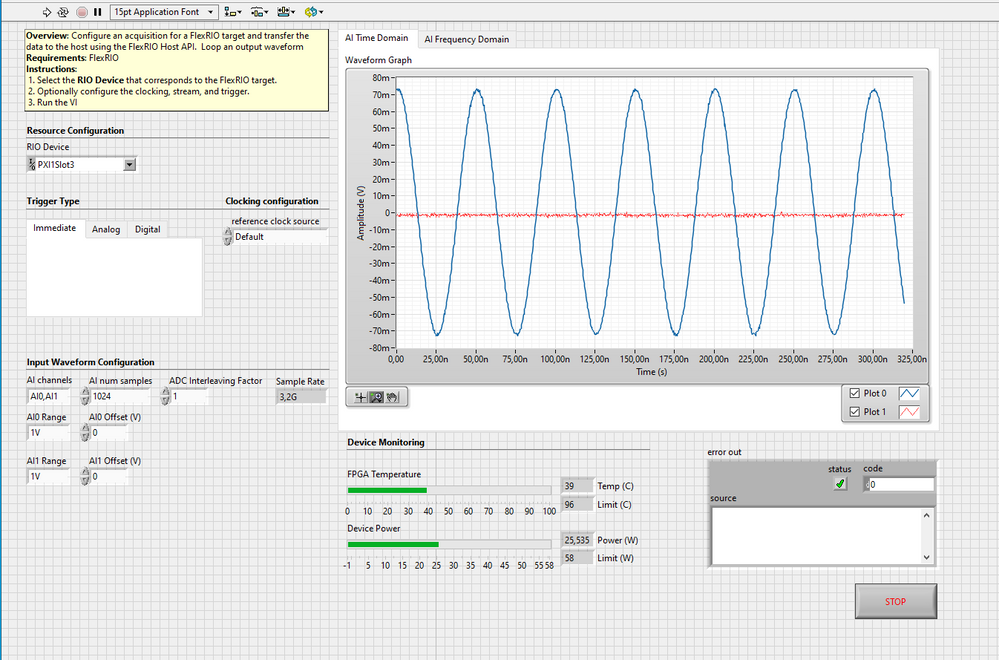

Thank you for your answer and to all others too. I am not a very good coder and I'm new to LabVIEW in particular thus the bad code. My signal is a "pure" 20 MHz sine-wave. I used the fpga to send me what it thinks the pure waveform looks like in the time domain before processing and it looks like this (The red signal is noise from the other input channel that is not sent to the host on the code that includes the FFT):

As far as I know that should produce a decent FFT, right?

Aarni

05-30-2023 01:01 AM - edited 05-30-2023 01:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I will look into your answer.

This code doesn't necessarily need all of the data but the ultimate goal is to produce a code that takes real signal coming from a laser and analyze it's frequency domain, average many frequency spectrums to one and send that data to the host to be further analyzed. So I need to use all 3.2 Gs every second but in the real implementation I will obviously not be sending all that data to the host.

This is my FFT configuration at this time. Yes I could increase the Blocklength:

I haven't talked to the sales representative as this device was purchased (but not used) before I came.

05-30-2023 01:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, it is obvious there is something wrong with your FPGA code.

I noticed another thing from your block diagram. You convert FFT results of X to +-,23,12, while Y to +-,23,1. I guess Y should be configured the same as X.

05-30-2023 01:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, thanks for you reply.

I'm not understanding what you mean by Y and X. The input to the FFT is +-,12,1 and the output is set to "adapt to source" so it produces a +-23,12 which I then shift the decimal point of the bit pattern to +-,23,1 which I think is unnecessary because fruther the FXP is converted to 32 bit interger and then to 16 bit interger by this code:

Aarni

05-30-2023 01:56 AM - edited 05-30-2023 02:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@IhmeKyselijä wrote:

Thank you for your answer and to all others too. I am not a very good coder and I'm new to LabVIEW in particular thus the bad code. My signal is a "pure" 20 MHz sine-wave. I used the fpga to send me what it thinks the pure waveform looks like in the time domain before processing and it looks like this (The red signal is noise from the other input channel that is not sent to the host on the code that includes the FFT):

As far as I know that should produce a decent FFT, right?

If this is exactly all the data that you are transforming, there is nothing "decent" about it!

Each bin in the frequency domain corresponds to an integer number of cycles over the sampling interval, so if you mentally take your interval and append it an infinite number of times, the FFT spectrum will not change. However, if you do that with your data, you can see that at the splice points there is an instant 180 degree change in phase, causing a gigantic jump (approximately from min to max!) that can only be modeled by a huge number of other frequencies. You need to ensure that all your frequencies have close to an integer number of cycles over the interval to be transformed (change sampling rate and time), and/or you need to use an suitable windowing function to lessen these sharp transitions.

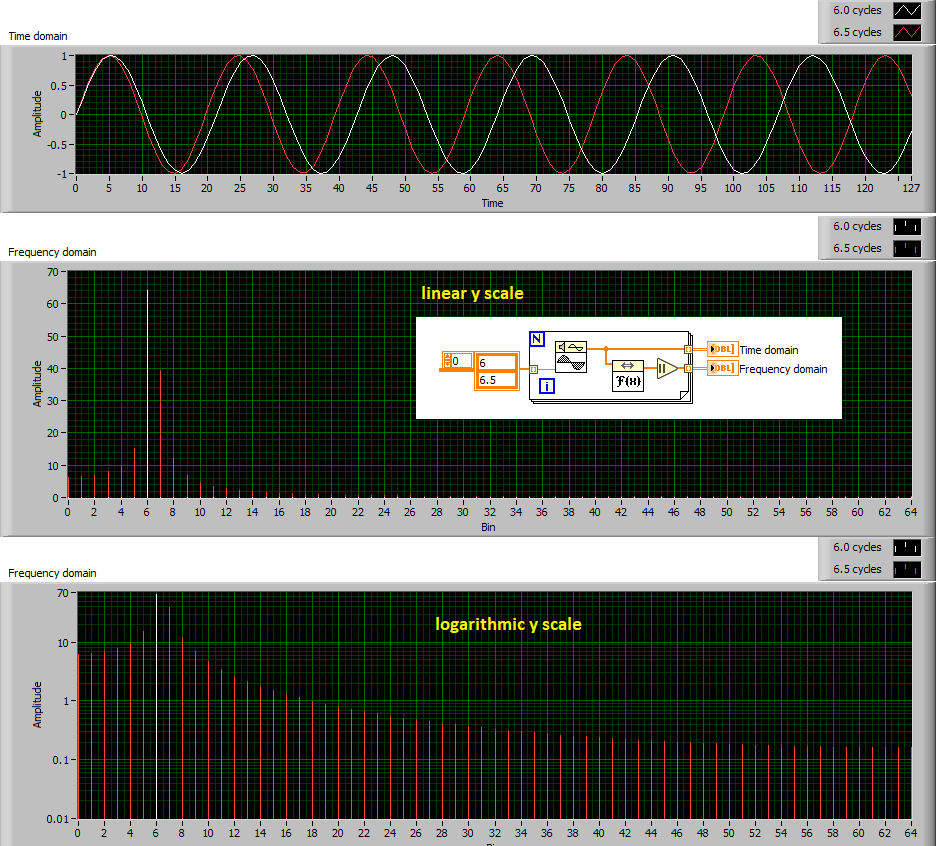

Here is a very simple illustration, showing the magnitude FFT of a pure sine function with either 6 or 6.5 cycles.

You can easily see that the red data gives results in a wide collection of frequencies. In fact ALL possible frequencies are nonzero!

05-30-2023 02:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@altenbach wrote:

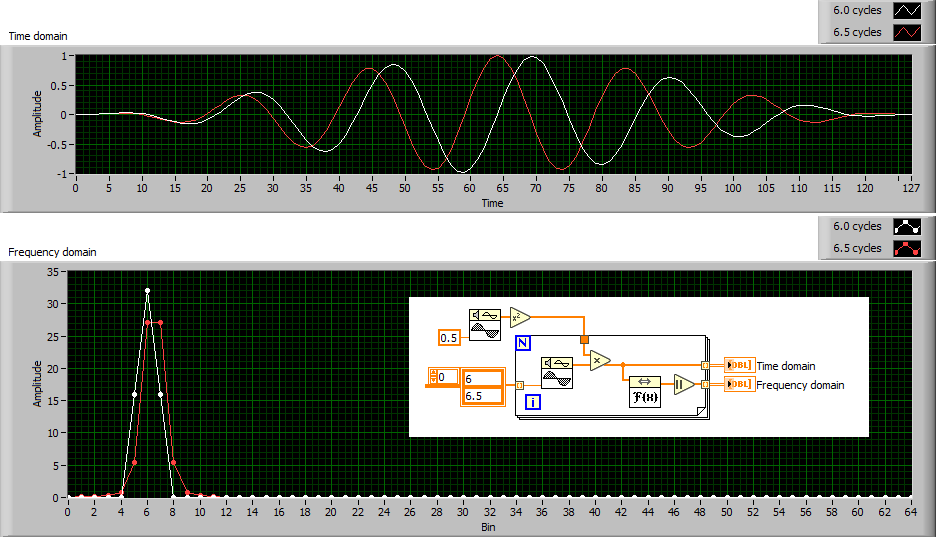

... or you need to use an suitable windowing function to lessen these sharp transitions

Just applying a simple windowing function (yes, there are many other windows, this is just for illustrations) to my example above will show similar width for both inputs. You can clearly see that the white is centered at 6.0 cycles and the red is centered at 6.5 cycles, both with similar widths.