FPGA Compilation Status Window doesn't show timings

Hello,

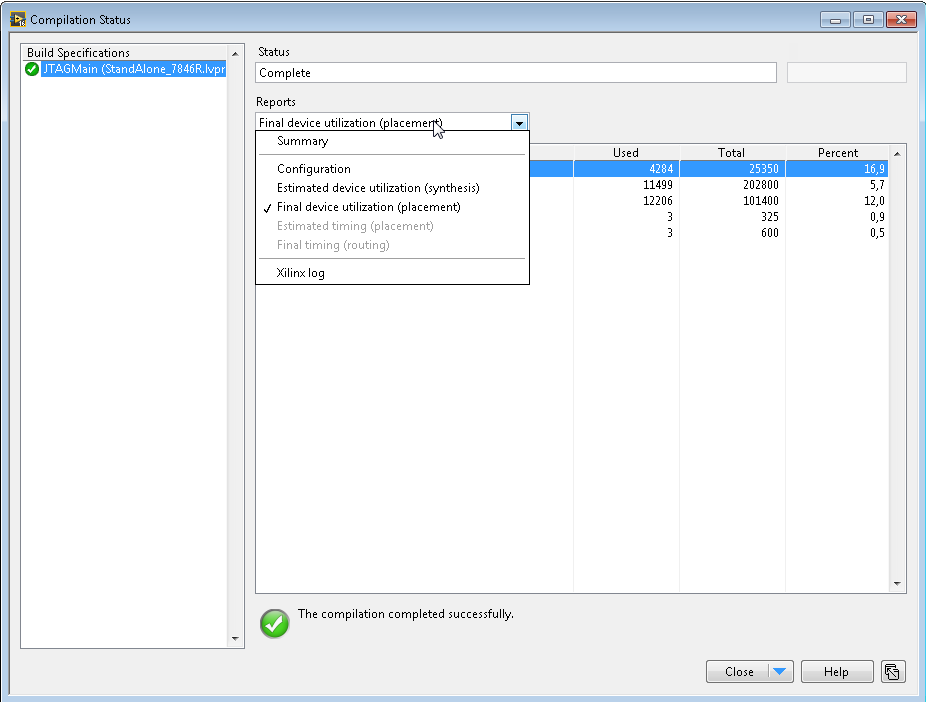

when compiling an FPGA project with LV2016 for PXIe 7846r, no timing information is displayed:

What could be the reason? Last year I compiled the same project for the PXI 7841r with LV2015SP1 and the timing information showed up just fine.

The code is working and doing what it's supposed to do (using the default 40MHz clock).

Thanks & Regards

Dirk

Hey Dirk,

There is certain hardware that does not display Estimated Timing data, for example FlexRIO. This is directly related to the files that are parsed to create these estimates, and whether the are available on the hardware, so my guess is PXIe 7846r is such a case.

Is there a specific reason this is causing issue, given the code is functioning correctly? or was it more curiosity?

Kind regards,

Rebecca

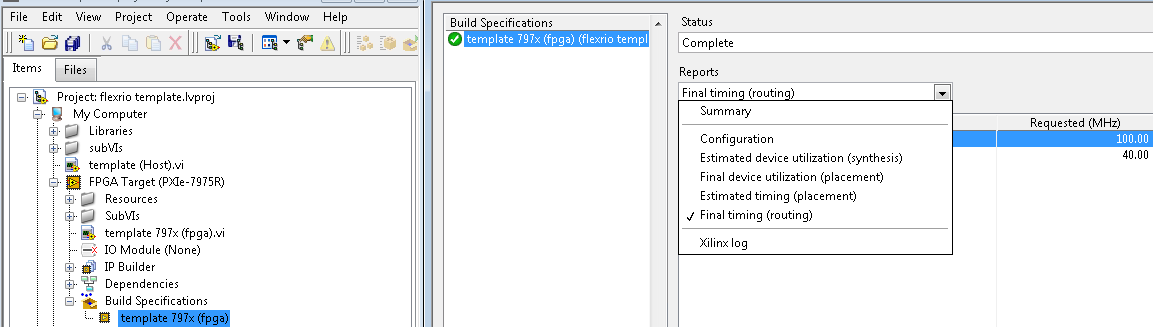

Weird that it completed successfully and didn't show the timing. I can see the final timing the the 7975 FlexRIO target I just compiled for.

If its not showing up there, you could try looking at the raw files that this report is pulled from. You can find them in: C:\NIFPGA\compilation\<SpecificCompilationFolder>\output_files.zip\<something>.twr

The twr file is the timing report file that is generated by the compiler and parsed by LVFPGA. It will be difficult to read if you're unfmailiar with fpga compilers, but it may have a lot more information depending on what it is you were trying to glean from report.

The TWR files for PXIe 7846r do not contain a "Timing summary" but the TWR files for PXI 7841r do.

I guess that LabView parses the that Timing summary section to fill the compilation window. So the question is, why is the timing summary missing? The 7841r uses ISE while the 7846r uses Vivado, so that could explain why the TWR files have different contents. But there must be a way to find out the maximum frequency....

The design is working well at 40MHz but I want to increase the frequency if possible. The higher the frequency, the better the "performance" of the design.

Regards

Dirk

Not sure why the timing summary is absent for that device. The timing summary is most useful when you've already violated timing somewhere and want more information about how much you've missed timing. I personally don't find it useful when exploring how much additional slack is available to ratchet up the clock speeds. When exploring faster clock speeds, I usually create 3 or 4 similar VIs, each with a different clock source, create a build spec for each of them, then kick off all the compiles at once.