- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[FPGA] Compilation Error - Slice LUTs size exceeded for simple program

12-18-2019 09:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, I am using LabVIEW 2016 with cRIO-9039 that has a FPGA Xilinx Kintex-7 7K325T with 203,800 LUT Slices.

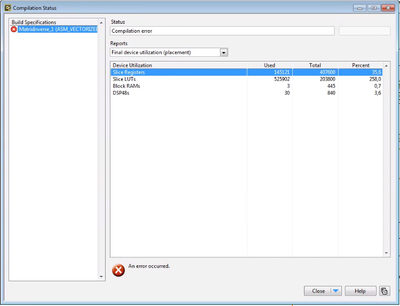

I am trying to implement a reasonably simple SPMI Matrix Inverse program into the FPGA, but I am getting error on compilation because it uses over 200% of the allocable LUTs. I understand that big arrays (mine has to be at least size 100) take a large amount of resources, but I've tried doing similar things before with these size arrays in the FPGA and wouldn't even take half of the resources. So I feel that something is wrong with my code and the understanding that the compiler does of my code.

Please find the attached VI (MatrixInverse_1.vi) with its subVIs, and the error pictures.

I also tried setting implementation strategy to "optimise area" but it did not solve the situation.

How can I further reduce the LUT usage in order to fit it into my FPGA?

12-19-2019 01:32 AM - edited 12-19-2019 01:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Boujuan,

@Boujuan wrote:

How can I further reduce the LUT usage in order to fit it into my FPGA?

Use FXP instead of SGL wires to reduce LUT usage…

Whatever happens in the TRUE case of the case structure should be done before the FOR loop…

Cleaning up the array dimensions: why do you need to multiply a array[10 elements] with an array[100 elements]?

Don't use a FOR loop when you just need a sequence frame (at the end)…

The subVIs ArraySubset and ArrayInMatrixExpander are very similar, you might merge them into one subVI…

ReplaceArraySubset is resizable, so you can simplify the last FOR loop inside the case structure…

Generic advice:

Cleaning up the whole VI might help to improve readability (and help for simplification)…

One subVI is missing from your upload.

When uplaoding several files it helps to ZIP them.

12-19-2019 05:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

Thank you for the advice, I will implement your suggestions and hope it will be enough.

About the multiplication of the 100 sized array with the 10 sized array, it is because I am handling 2D matrices as 1D arrays,

so the 100 sized array is actually a 10x10 matrix being multiplied by a 10 vector.

12-19-2019 06:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Boujean,

@Boujuan wrote:

so the 100 sized array is actually a 10x10 matrix being multiplied by a 10 vector.

No, the place I found is a simple multiplication of an array[100] with an array[10], which is simply overkill in the FPGA…