- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Clock Accuracy

01-04-2021 02:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Is there any way to make the FPGA clocks more accurate? I am hoping to get to 50 ppm.

I am using the 7972 FPGA which apparently has an accuracy of 100 ppm. I have it in the 1095 chassis which apparently has an accuracy for the 10MHz backplane of 25 ppm. Isn't the 10 MHz clock from the FPGA synchronized and derived from the 1095 backplane? Is there any way I could improve my FPGA's derived clocks accuracy using the backplane/chassis?

Any insight would be appreciated.

Thank you

01-04-2021 03:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sure, you can use the chassis clock as a reference to have a better timing reference.

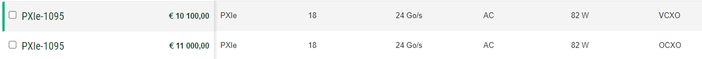

Make sure however that your 1095 chassis has the 25 ppm clock otherwise you will be using a poorer clock as you can see below (extracted from ni.com) :

However, you will have to configure your reference clock in the LabVIEW software using the Flexrio instrument library (If anyone can clarify further the vi's name) .

Otherwise, if you have more stringent clock accuracy requirements, you can always add a synchronization module to your chassis and use it as the timing reference.

01-04-2021 04:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Building off of mourad's post, for the 7972R you shouldn't have to do anything special to sync the FPGA clock to the chassis.

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA03q000000YHkYCAW&l=en-US

01-05-2021 06:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Jacobson-ni wrote:

Building off of mourad's post, for the 7972R you shouldn't have to do anything special to sync the FPGA clock to the chassis.

But that syncing seems to be done through a PLL, not direct clock connection. A PLL will always introduce some jitter, so it might not be possible to get 50 ppm that way.

01-05-2021 06:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@mourad_FAKHFAKH wrote:

Sure, you can use the chassis clock as a reference to have a better timing reference.

Make sure however that your 1095 chassis has the 25 ppm clock otherwise you will be using a poorer clock as you can see below (extracted from ni.com) :

However, you will have to configure your reference clock in the LabVIEW software using the Flexrio instrument library (If anyone can clarify further the vi's name) .

Otherwise, if you have more stringent clock accuracy requirements, you can always add a synchronization module to your chassis and use it as the timing reference.

So with the my chassis, I have it synced to an external clock (I have a 10 MHz clock going into it to PLL to via a timing/sync card and ni sync). If my timing source is highly accurate, do the chassis inherit its accuracy? From the commenter after yours, it sounds like it doesn't? Is there any way to quantify the new accuracy?

01-05-2021 06:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Jacobson-ni wrote:

Building off of mourad's post, for the 7972R you shouldn't have to do anything special to sync the FPGA clock to the chassis.

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA03q000000YHkYCAW&l=en-US

This appears to be out of date? My labview doesn't have the "Synchronize FPGA clock to PXI_Clk10" option anymore in "RIO Device setup", but I believe it automatically does that from prior testing.

01-05-2021 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@bchang32 wrote:

@Jacobson-ni wrote:

Building off of mourad's post, for the 7972R you shouldn't have to do anything special to sync the FPGA clock to the chassis.

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA03q000000YHkYCAW&l=en-US

This appears to be out of date? My labview doesn't have the "Synchronize FPGA clock to PXI_Clk10" option anymore in "RIO Device setup", but I believe it automatically does that from prior testing.

I think that part is only relevant to some specific versions of the RIO driver and even then is only required for R-Series boards in those versions.

01-05-2021 09:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@bchang32 wrote:

@mourad_FAKHFAKH wrote:

Sure, you can use the chassis clock as a reference to have a better timing reference.

Make sure however that your 1095 chassis has the 25 ppm clock otherwise you will be using a poorer clock as you can see below (extracted from ni.com) :

However, you will have to configure your reference clock in the LabVIEW software using the Flexrio instrument library (If anyone can clarify further the vi's name) .

Otherwise, if you have more stringent clock accuracy requirements, you can always add a synchronization module to your chassis and use it as the timing reference.

So with the my chassis, I have it synced to an external clock (I have a 10 MHz clock going into it to PLL to via a timing/sync card and ni sync). If my timing source is highly accurate, do the chassis inherit its accuracy? From the commenter after yours, it sounds like it doesn't? Is there any way to quantify the new accuracy?

Let's try and disentangle a couple of topics here. Refresher: https://www.ni.com/en-us/support/documentation/supplemental/06/what-clock-error-means-to-your-measur...

1) What clock accuracy is required for your application? This can be increased from stock 7972 by using a high accuracy frequency reference to your chassis 10MHz input, or by introducing an NI timing card. Your clocks in the FPGA must all be derived from that 10 MHz then, and the accuracy should propagate. If you need a 10 MHz clock and you've got a 25ppm oscillator, then that means your clock freq might be between 9.999750MHz to 10.000250MHz but does NOT imply jitter (separate spec for your oscillator).

2) What Jitter is required for your application? The PLLs in the 7-series add a minimum of 50ps of jitter, which is on top of the jitter of your oscillator. Unless you're running your base clock, or a SCTL off of that 10 MHz input, there will be a PLL inserted in-line between your clock source (highly accurate 10 MHz) and your actual logic, and therefore more jitter.

01-05-2021 10:50 AM - edited 01-05-2021 11:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@JJMontante wrote:

1) What clock accuracy is required for your application? This can be increased from stock 7972 by using a high accuracy frequency reference to your chassis 10MHz input, or by introducing an NI timing card. Your clocks in the FPGA must all be derived from that 10 MHz then, and the accuracy should propagate. If you need a 10 MHz clock and you've got a 25ppm oscillator, then that means your clock freq might be between 9.999750MHz to 10.000250MHz but does NOT imply jitter (separate spec for your oscillator).

So I need a 80MHz clock with +/- 50 ppm. I have a CLIP that generates an 80MHz clock using a frequency of 160 MHz.I have an ntp server sending 10MHz to the backplane for the chassis to sync to. When I look at the accuracy of the clock in the file explorer, it says 100 ppm which is worse than the chassis 10MHz as well as ntp 10MHz which is causing me some confusion.

2) What Jitter is required for your application? The PLLs in the 7-series add a minimum of 50ps of jitter, which is on top of the jitter of your oscillator. Unless you're running your base clock, or a SCTL off of that 10 MHz input, there will be a PLL inserted in-line between your clock source (highly accurate 10 MHz) and your actual logic, and therefore more jitter.

I don't think a jitter is specified for my application. The device I'm trying to interface to just says the aforementioned 50 ppm accuracy.

01-05-2021 12:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@JJMontante wrote:

Let's try and disentangle a couple of topics here. Refresher: https://www.ni.com/en-us/support/documentation/supplemental/06/what-clock-error-means-to-your-measur...

1) What clock accuracy is required for your application? This can be increased from stock 7972 by using a high accuracy frequency reference to your chassis 10MHz input, or by introducing an NI timing card. Your clocks in the FPGA must all be derived from that 10 MHz then, and the accuracy should propagate. If you need a 10 MHz clock and you've got a 25ppm oscillator, then that means your clock freq might be between 9.999750MHz to 10.000250MHz but does NOT imply jitter (separate spec for your oscillator).

I need 50 ppm accuracy at 80MHz. I know the 1095 chassis has 25 ppm accuracy, but I have an external 10MHz being PLL'd into the chassis since I have more than one chassis I need to sync to. My concern is that when I look up the clock accuracy in the Labview FPGA file explorer (via the properties tab), it says 100 ppm. How does it be 100 ppm when the 1095 chassis has 25, the timing card I have has 80 ppb, and I believe my NTP server providing the 10 MHz input has around 25/50 ppm as well.

2) What Jitter is required for your application? The PLLs in the 7-series add a minimum of 50ps of jitter, which is on top of the jitter of your oscillator. Unless you're running your base clock, or a SCTL off of that 10 MHz input, there will be a PLL inserted in-line between your clock source (highly accurate 10 MHz) and your actual logic, and therefore more jitter.

The jitter is not specified. I just need high accuracy. I imagine it occasionally being off it ok as long as it has 50 ppm accuracy.

From looking at your doc, it doesn't seem like I can do much to improve it? I can't change the oscillator and I imagine re-calibration wouldn't get me from 100 ppm to 50ppm?