- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Dynamically decimate data from synchronized modules

06-04-2018 01:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear NI community,

let me, please, ask about the following.

I'd like to acquire data at FPGA from NI 9237 and 9234 modules. I'd like to have it synchronize by master clock from 9234 module. But, I'd like to acquire data with separate sampling rates. For example, NI 9234 with 51.2 kS/s, and at the same time NI 9237 with 3.2 kS/s.

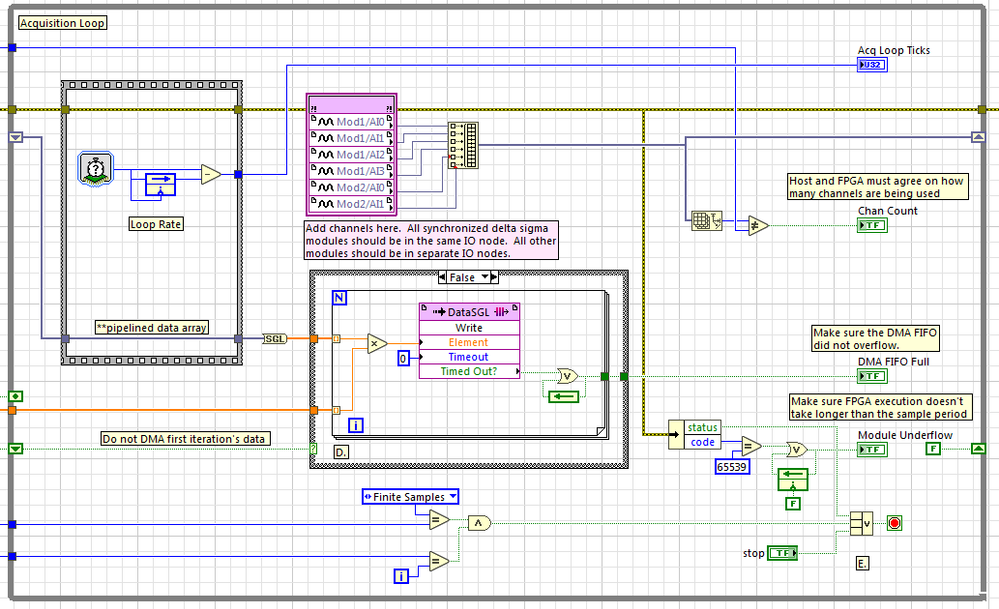

If I'll place it into one while loop, as in community examples (see attached screenshot), then I need to run them at the highest sample rate (or not?), and then decimate data. Please, are there some examples of how to dynamically decimate data? Because sampling rates could be any from the allowed selectable range... I've found Decimate function at FPGA pallete, but it should have fixed configuration, not on-the-fly...

Where would be more effient to have decimation - at FPGA side, or at cRIO side?

Or, then it is better for each module implement separate while loop?

Thanks a lot in advance,

Sincerely, kosist90.

06-06-2018 04:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

One way I can think of doing that is index of loop and then divide by a number and when that equals 0 take the data at that point.

Parul M.

Applications Engineer

National Instruments