- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Data missing from TDMS file

03-21-2018 04:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

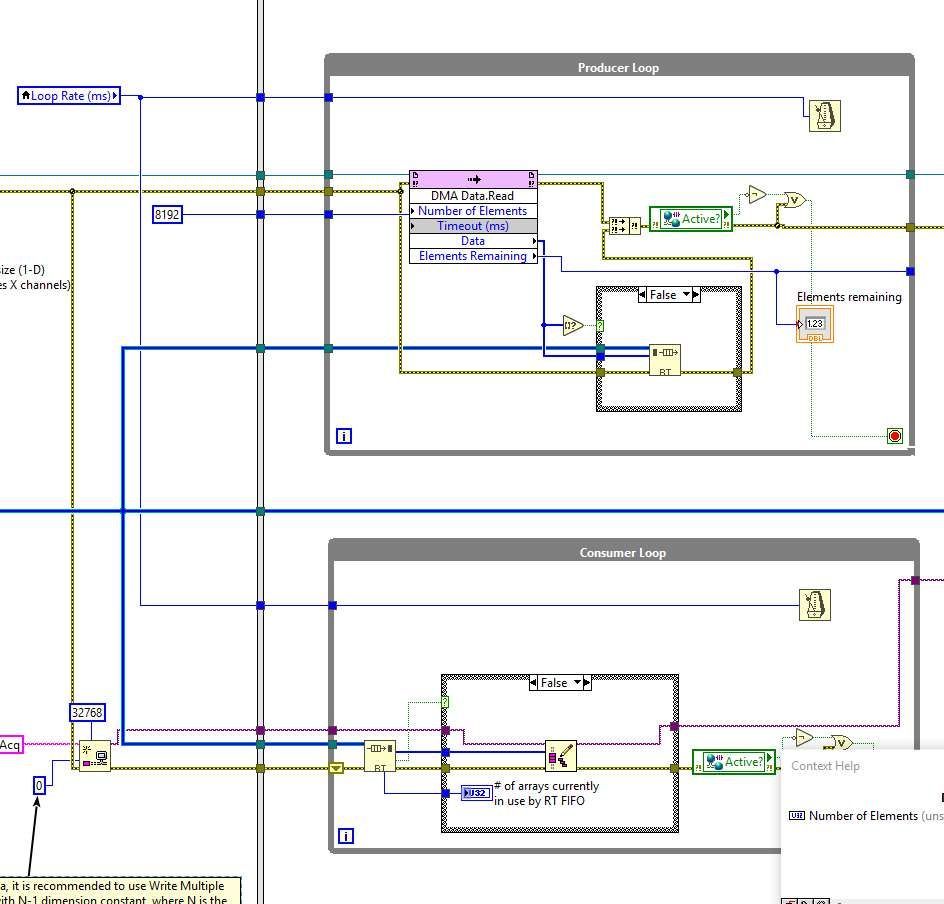

I have written an application that collects TDM data (essentially a single channel of I2S) from 16 serial connected microphones using a myRIO-1900. The application consists of three VIs. TDM Decoder.vi runs on the FPGA on the myRIO. It collects and sends data using DMA to a Real-TIme Main.vi running on the myRIO. Real-Time Main.vi uses a producer/consumer loop and network streams to send data to TDM Data.vi running on the host computer. TDM Data displays the waveforms and stores the data to a TDMS file.

I am having issues with missing data.

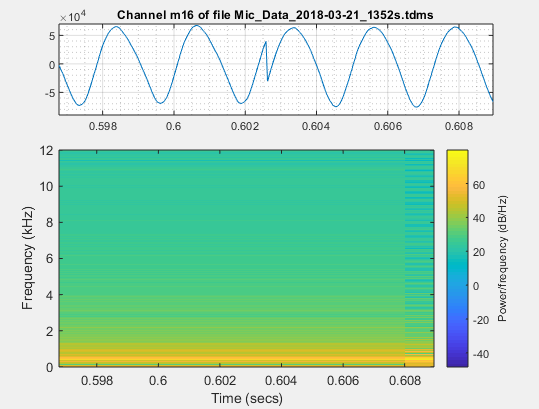

The plot above shows a discontinuity in the TDMS data file. I have played around with adjusting the size of the DMA buffer, the producer/consumer loop rate and the number of elements in each interation of the producer without being able to get rid of the discontinuities.

Anyone have some thoughts on how to troubleshoot and fix this problem.

Thanks,

Douglas

03-21-2018 04:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I doubt the problem is with your TDMS file. I would look at your communication methods. Make sure you are overrunning your DMA with data in the communication between the FPGA and RT. Look at the network stream between the RT and the PC host.

03-22-2018 07:48 PM - edited 03-22-2018 07:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

On further analysis it appears the data loss occurs between the FPGA and RT. I determined this by changing the loop rate of the producer/consumer loop in the RT. The data gaps occur at the loop rate. The DMA buffer for these data on the FPGA is set to 32767, which is much larger than is needed. This is a 16 channel system sampling at 24kHz generating 384000 samples / second. For a 10ms producer/consumer loop rate the system should produce 3840 samples. The producer reads up to 8192 values from the DMA on each loop iteration, but it is still missing data.

Thoughts?

03-22-2018 08:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Consumer loops should not have anything that throttles their rate. Get rid of the wait timer in there. You want it to run as fast as it can so it can catch up with the data coming into it from the producer in case it ever falls behind.

Double check all of your timing mechanisms. The architecture seems very fragile in the number of queues and transfer mechanisms you have. I think I even missed one when I first looked at it.

You have:

DMA FIFO. From FPGA to RT

RT FIFO from producer to consumer in RT Main (do you really need this one?)

Network stream from RT to Host.

I only think you need the DMA and the Network stream so that you get data from FPGA to RealTime, Then from realtime to Host. The more transfer paths you have, the trickier it will be making sure any given one doesn't fill up or run dry causing a chain reaction in the whole chain.

PS: In the host VI, you are using a decimate array wired to a Build array to turn a 1-D into a 2-D array. It seems to me it would be a lot easier if you used Reshape Array.