- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Crossing Clock Domains in the FPGA Examples

Solved!11-18-2014 11:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I was looking through some of the LabVIEW FPGA Examples and I came across the Crossing Clock Domains Example.

In this example there exists 4 VIs; FIFOs.vi; Global Variables.vi; Local Variables.vi; and Registers.vi. In each of these VIs there is a timed-loop that runs at 160 MHz.

How is this possible? Since the clock on the FPGA is only 40 MHz. Am I missing something?

Staff Test Systems Engineer

Woodward, Inc.

Skokie, Illinois, USA

"Life is not a journey to the grave with the intention of arriving safely

in a pretty and well preserved body, but rather to skid in broadside,

thoroughly used up, totally worn out, and loudly proclaiming...

Wow...What a Ride!"

Solved! Go to Solution.

11-18-2014 11:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

On the FPGA target you can right-click the 40MHz clock and create a derived clock which can be a multiple of or a fraction of the base clock (40MHz).

160MHz is a trivial example of 4 times the base clock.

12-20-2017 08:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

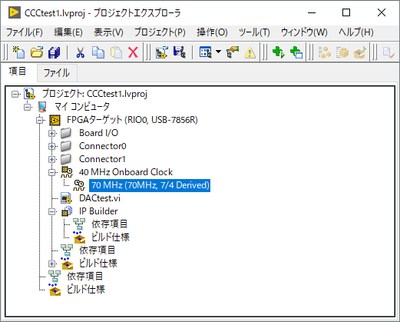

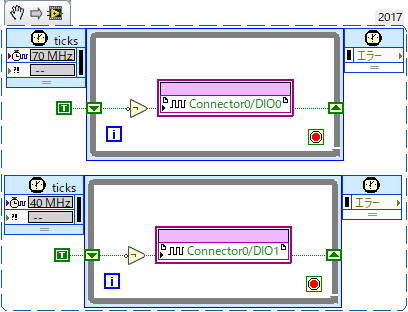

I could make a derived clock frequency as shown below(sorry in Japanese), but I couldn't know how to use it.

I tried to drug&drop DACtest.vi under the derived 70 MHz clock, and I also tried to move I/O there, I couldn't do that.

Thank you for your kind help,

moge

12-21-2017 09:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi moge,

If you are using a timed loop in your application and you double-click on the input node of the timed loop it will allow you to select your timing source. This is where it will let you choose a clock other that your top level clock.

Hope this helps.

Staff Test Systems Engineer

Woodward, Inc.

Skokie, Illinois, USA

"Life is not a journey to the grave with the intention of arriving safely

in a pretty and well preserved body, but rather to skid in broadside,

thoroughly used up, totally worn out, and loudly proclaiming...

Wow...What a Ride!"

12-22-2017 07:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your kind reply.

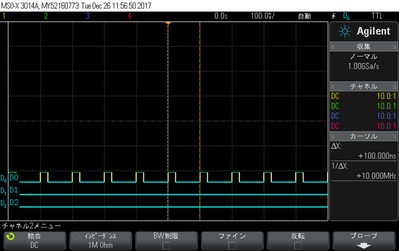

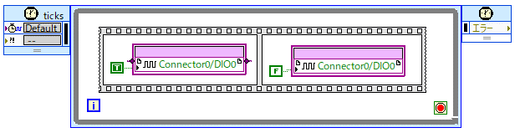

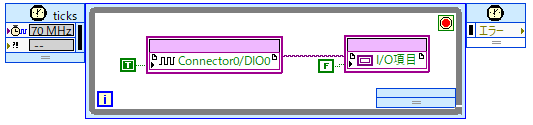

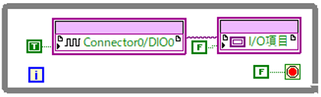

I could chose derived clock frequency as below.

I assumed that below diagram generates continuous 35 MHz clock, but it doesn't work well.

If possible, please tell me how I can generate 35 MHz(70 MHz/2) clock.

Thanks for your kind help,

moge

12-25-2017 11:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It's additional detail.

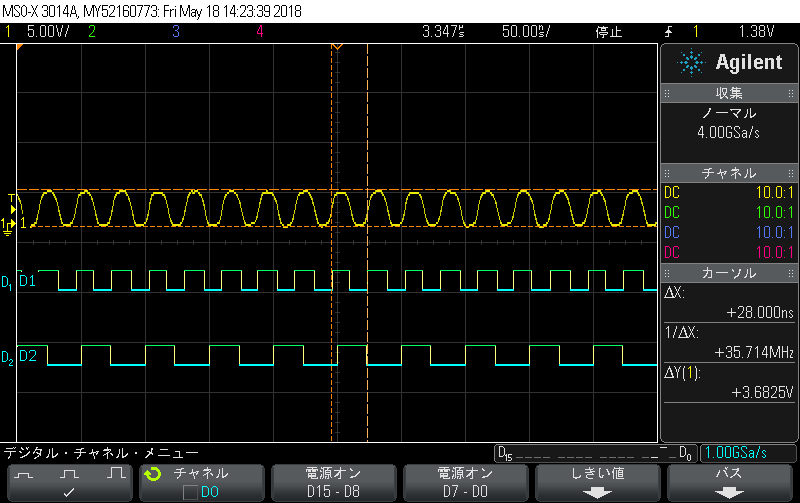

By below left diagram, I could get right result.

My USB-7856R output 10 MHz continuous clock.

The duty ratio was 0.26 (26 ns + 74 ns = 100 ns).

Then I changed the while loop to the timing loop as shown below.

In above diagram, I used top-level timing source (80MHz) and the result was below.

My USB-7856R output pulses disorderly for 342 ns, then went high.

I restarted the vi to check the repeatability of this strange operation, but the output remained Hi level (didn't change).

I couldn't observe any pulse after I recompiled same diagram.

If possible, please point out the problem or tell me the other way to use derived clock.

I'm using:

LabVIEW2017 professional development system (ver.17.0f2) 32-bit on Windows 10 pro

NI USB-7856R R series Multifunction RIO

Thank you for your kind help,

moge

01-03-2018 09:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This is an FPGA so you do not want to write to the same port twice in the same clock cycle.

My recommendation would be to set your source to a derived clock of 70Mhz for a 35 MHz continuous clock. Then toggle the pin on every clock cycle. This should give you a 35 MHz signal with a 50% duty cycle.

The duty cycle can be controlled by inserting a case structure with a different wait time for each state.

Staff Test Systems Engineer

Woodward, Inc.

Skokie, Illinois, USA

"Life is not a journey to the grave with the intention of arriving safely

in a pretty and well preserved body, but rather to skid in broadside,

thoroughly used up, totally worn out, and loudly proclaiming...

Wow...What a Ride!"

01-03-2018 11:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Also, there may be example code that shows better how to generate an output. For some I/O, you must have them in a loop that runs based on the IO Clock otherwise you may end up out of phase (especially for analog I/O).

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

05-18-2018 01:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear johnoc and Terry,

Thanks for your kind replies and I'm sorry for this really rate reply.

I couldn't try this for about 5 months for other jobs.

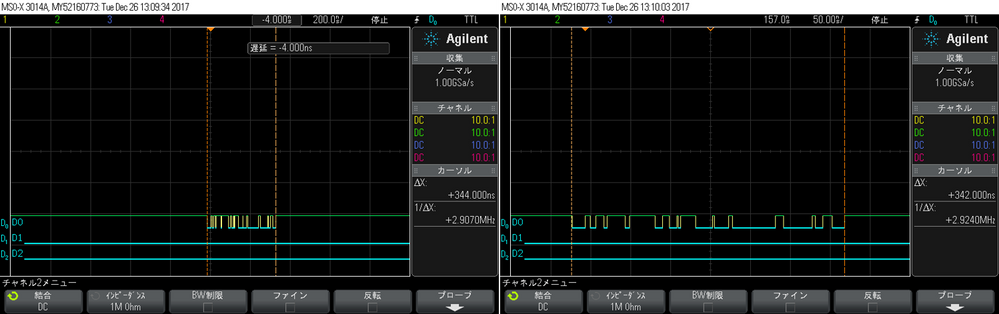

With below diagram, I've succeeded to output 35 MHz and 20 MHz clock as shown below.

I changed my diagram to "toggle type" as johnoc said.

As Terry said, the synchronization is the next problem.

I'll try to search good sample.

Thanks for your kind help,

Best regads,

moge