- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Compilation Error: Xilinix [DRC LUTLP-1] Combinatorial Loop Alert

12-12-2018 08:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Good morning everyone,

I'm facing some troubles when compiling my PXIe FlexRio board. In particular, at the end of the (long) compilation process, i obtain the following error:

"ERROR: [DRC LUTLP-1] Combinatorial Loop Alert: 15 LUT cells form a combinatorial loop. This can create a race condition. Timing analysis may not be accurate. The preferred resolution is to modify the design to remove combinatorial logic loops. If the loop is known and understood, this DRC can be bypassed by acknowledging the condition and setting the following XDC constraint on any net in the loop: 'set_property ALLOW_COMBINATORIAL_LOOPS TRUE [net_nets <myHier/myNet>'."

I really don't understand why this happens (and what does it means), since when I compile the same code on a PCIe 7821R everyting goes fine.

Thanks in advance,

ALST

12-28-2018 05:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ALST,

can you please send your project in attachment, so we can try to reproduce the error on our side? Or at least, can you share the full Xilinx report? It may contain information that can help us to narrow down where the combinatorial loop comes from.

I look forward to hearing from you.

Regards,

Alessia

01-09-2019 01:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have the same problem when using FlexRIO 7935 and 1483.

ERROR: [DRC LUTLP-1] Combinatorial Loop Alert: 1 LUT cells form a combinatorial loop. This can create a race condition. Timing analysis may not be accurate. The preferred resolution is to modify the design to remove combinatorial logic loops. If the loop is known and understood, this DRC can be bypassed by acknowledging the condition and setting the following XDC constraint on any net in the loop: 'set_property ALLOW_COMBINATORIAL_LOOPS TRUE [net_nets <myHier/myNet>'. The cells in the loop are: NI1483Corex_i_3.

......

ERROR: [Vivado 12-1345] Error(s) found during DRC. Bitgen not run.

5 Infos, 74 Warnings, 0 Critical Warnings and 2 Errors encountered.

write_bitstream failed

::ERROR: [Common 17-39] 'write_bitstream' failed due to earlier errors.

while executing

"write_bitstream -force -bin_file -no_binary_bitfile "SmallBlockTop""

(file "C:/NIFPGA/jobs/VGyA9CV_AAa8N4o/bitgen.tcl" line 28)

invoked from within

"source "C:/NIFPGA/jobs/VGyA9CV_AAa8N4o/bitgen.tcl""

# exit

INFO: [Common 17-206] Exiting Vivado ...

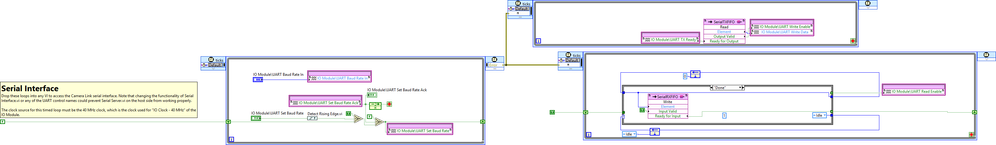

And My code is really simple, I just rewrite the Serial control in for 1483, the example provided lot of stuff I don't need, so I just keeps the Tx and Rx and wire them to host fifo.

01-09-2019 01:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

By disable the set baud rate loop, my code finishes compilation.

Maybe there are something to do with the driver, I'm not sure, at least it works now.

01-14-2019 05:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I think the problem is that there's no feedback node anywhere on the path from "UART Set Buad Rate Ack" to "UART Set Baud Rate". The input "UART Set Baud Rate" causes "UART Set Buad Rate Ack" to update combinatorially, so if there's no feedback node then you get a combinatorial loop.

I think it is sufficient to add a single feedback node directly to the output of "UART Set Baud Rate Ack" to fix your problem. This will split the combinatorial path.