- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

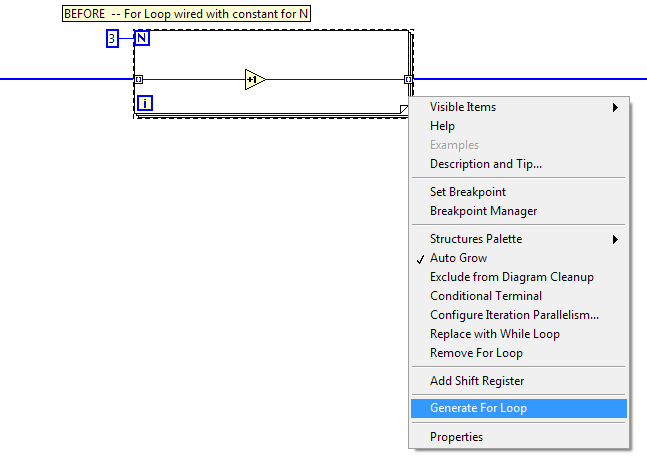

For Loop - Generate.llb (for FPGA code generation)

Author: AristosQueue (NI)

This plug-in works on For Loops that are wired with a constant for the N terminal. It is useful mostly to FPGA users who wish LabVIEW had a Generate Structure.

Generate Structures would have syntax very similar to For Loops, but their compiled behavior is very different.

Short version:

A For Loop is N calls to the same block diagram. Think of the loop's diagram as a NON-REENTRANT SUBVI.

A Generate Structure is N calls to N different block diagrams. Think of the loop's diagram as a PREALLOCATED REENTRANT SUBVI.

Long version:

Many users know about For Loop "unrolling" -- a compiler optimization where you peel off one or more iterations from the beginning or end of a loop and generate special code for them. You might even unroll the entire loop for parallelization. But For Loop unrolling still assumes that the results need to be the same as running the iterations sequentially.

With generation, the results are not the same. Iterations are assumed to not depend upon each other -- the array input can be deaggregated and acted on entirely without information from the other frames, but the entire structure may have state that is rememberd call over call. In other words, an uninitialized shift register on (or Feedback Node inside) a For Loop means "use this value when the For Loop is next called AND use every value from the previous iteration in the next iteration". The uninitialized shift register on a Generate Structure would mean "use this value when the Generate Structure is next called ONLY".

This menu shortcut provides an editor operation that provides a fast way to script the behavior a Generate Structure would have.

The "For Loop - Generate.llb" adds a new menu item means "Generate For Loop" to take the code that is expressed in a For Loop and replicate it N times. The original code is retained in a Diagram Disable Structure, so if you need to edit the original code, just remove the disable structure, edit the original, and regenerate.

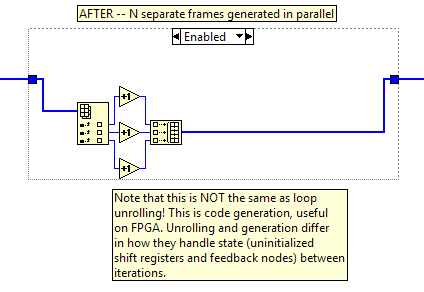

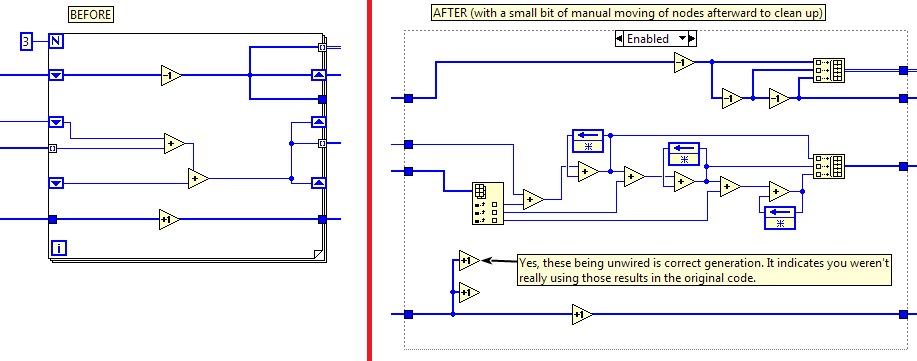

Two examples are shown below -- a simple one so you get the idea what is happening and a more complex one to show off how complex the generation can get once state is involved.

Example 1:

Example 2:

Notice the original has four wired inputs and four wired outputs. The generated code has the same, with the same types. The only thing that changes is how those values are computed. Don't try to read the For Loop as a For Loop. Instead, pretend it is a Generate Structure, as described above.

Attachement is saved in LabVIEW 2015. For install instructions, go here.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Amazing piece of kit! I'd attempted to use a for-loop in this manner recently, but run into numerous synthesis issues. Specifically items like array manipulation that aren't allowed to exist inside of a for-loop at synthesis time, that would be a natural use of generate statements in VHDL.

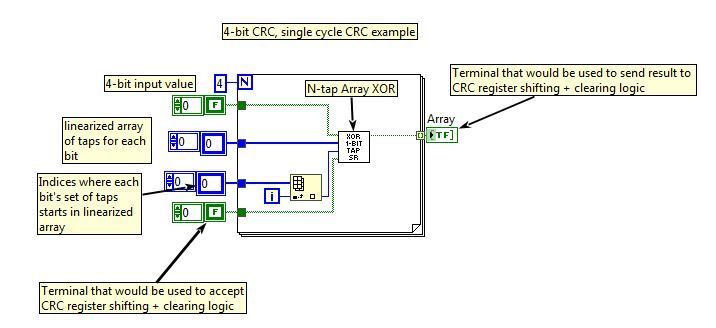

Do you have a suggestion on how to handle loop-iterator terminal items? For instance, suppose I have an array acting as ROM - linearized from a 2D array to a 1-D array because labview FPGA doesn't like 2D array types. In VHDL, I would typically use a generate statement along with a "stride" to parse that array into pieces to send to the generated logic. Here's an example of a 4-bit unrolled parallel CRC function.

Loop before unrolling:

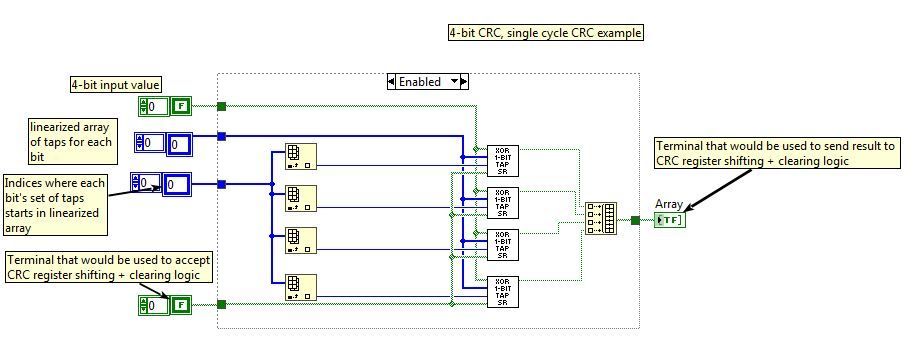

Loop after unrolling:

Notice that this would not give equivalent behavior since the for-loop iteration terminal has been removed, but not replaced with similar functionality. Putting a shift register + adder into the design creates a VERY long adder-chain for high iteration counts. For instance, extending this 4-bit CRC into a 32-bit CRC is unlikely to make timing. So Two alternate ways to get this functionally equivalent to the original loop would be as follows:

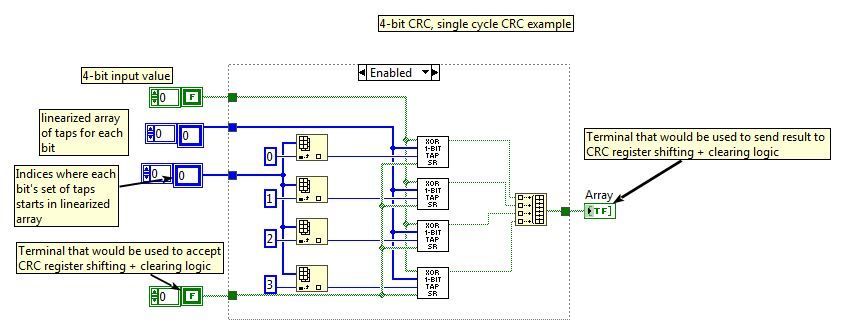

Method 1: Unrolled loop terminal

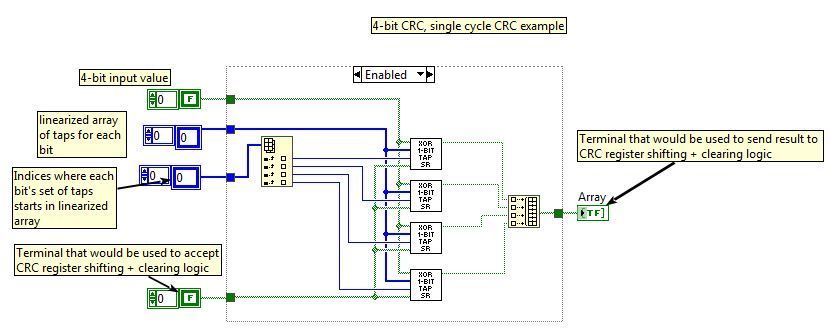

Method 2: Auto-generated 'array index' block.

Do you see any better (automated or otherwise) mechanisms for handling the notion of "stride" in a linearized array in LabVIEW FPGA? Using a pre-computed set of indices into the linearized array gets around having to do anything other than increment - but I still need to index into each element of that indices array.

Thanks for any suggestions you might have. Unfortunately I found this tool this morning, rather than last night when I put hours into manually parallelizing loops for unwieldly amounts of replication after finding simulatable models didn't allow synthesis (though equivalent vhdl constructs would be synthesizable).