- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Unit testing FPGA sub VI with feedback node inside (error -61449)

08-22-2015 01:25 PM - edited 08-22-2015 01:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Folks,

I'm trying to find out how to simulate an FPGA subVI on my desktop so that (a) I can call my unit test automatically and (b) not modify the code under test for the purposes of functional validation ((I'm happy to build a testbench around it). It would seem that the desktop execution node should do this, but I face problems with code that has internal feedback registers. Specifically, I would like to input an array that represents the vector's input cycle by cycle and then analyze an output waveform.

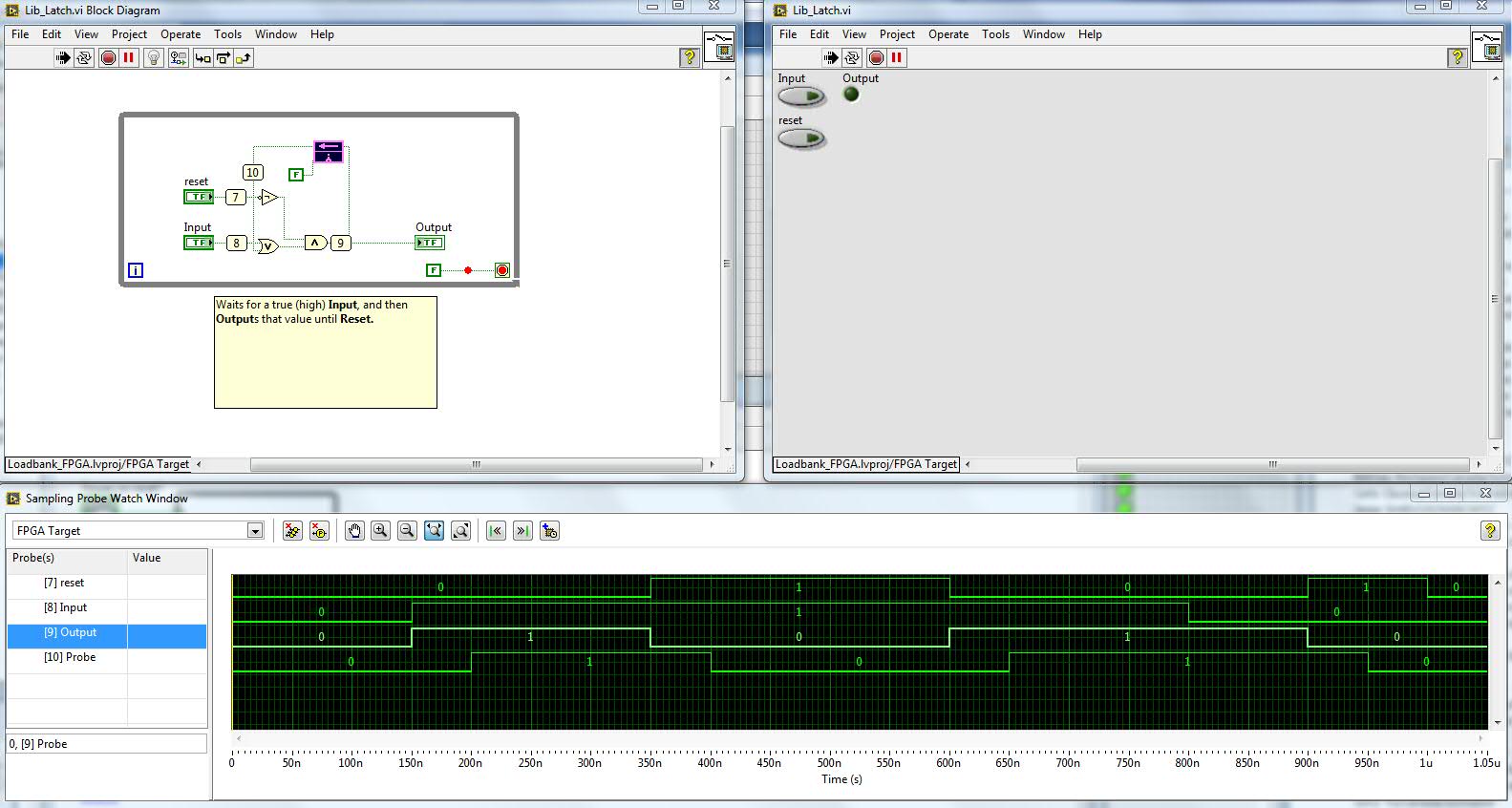

I've included a screencap of the manual way I do it now, basically by adding a while loop around my code, and putting a breakpoint after each iteration, and then adjusting the front panel controls. One might think of ModelSim by Mentor Grapics as to what I'm trying to achieve, but in a very basic way, such that I could say run the code from the Unit Test Framework.

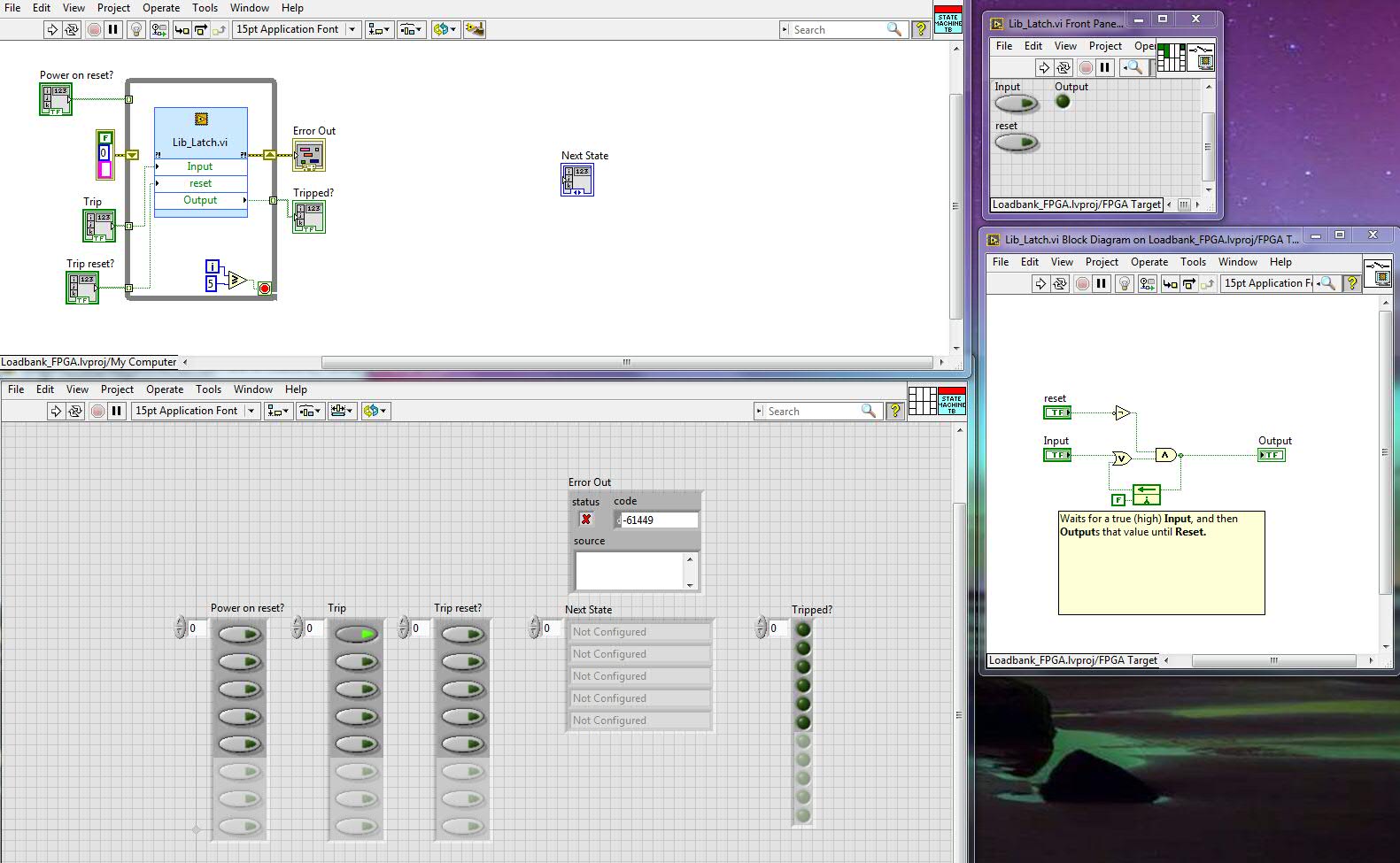

Just to clarify, this is where I would like to end up if I test the simple latch as above, but I keep getting error -61449

08-24-2015 05:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Rik,

I was able to recreate your code on my computer with no errors. I'm curious to see when the error starts to occur, as we are currently only seeing the last error from the while loop. Try changing the shift register to an indexing terminal to receive an array of error clusters.

Additonally, what FPGA target are you using?

08-26-2015 10:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you right-click the error cluster, and select 'Explain Error...', you get "LabVIEW FPGA: The FPGA VI has finished executing."

So, you may just need to move the .vi you used for testing into the context of the FPGA (drag & drop it into the FPGA in the project explorer). As it stands, the FPGA starts, runs the program once, then shuts down. A second run (if it hadn't stopped on an error) would have restarted from initial conditions, including the feedback node.

CLD, CPI; User since rev 8.6.