- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 5772, using clk_in as an external clock

07-02-2013 02:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi.

I'm using NI 5772R with NI PXIe-7966R NI FlexRIO FPGA Module.

I'm trying to sample the signal with external clock (CLK_IN). An example file 'Clock Select (FPGA).vi' is successfully compiled. However when running 'Clock Select (host).vi', the data doesn't seem to be sampled with CLK_IN signal even if I choose the clock source as 'External Clock'. Actually externally clocked data is the same as internally clocked data.

So I wonder if this is because the signal plugged into 'CLK_IN' has wrong range. The frequency range of my CLK_IN signal is 80~160MHz, while the specification of NI5772 says the CLK_IN input range is 400-800MHz. Would it be a problem?

Also, My clock signal is sinusoidal, rather than TTL. Does the CLK_IN need to be TTL?

Thanks for your help.

07-02-2013 02:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Kellerman!

I want to make sure I understand what's going on, it sounds like you've specified the clock to be external, you have provided it with an external clock, but it is still using the internal clock. Is that accurate? Are you determining this by providing a known signal and counting the samples per period?

The 5772 is not going to function properly if you do not provide it with a clock in the specified range. Could you multiply up your clock and decimate the unneeded data?

Finally, a sine will work fine for the clk in as long as it meets the specification

Input voltage range ...........................................+2 dBm (800 mVpk-pk) to +16 dBm (4 Vpk-pk)

Dave T

FlexRIO & R-Series Product Support Engineer

07-02-2013 02:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Dave,

I think you undersood correctly. I determined the difference between internal and external by counting number of data per period. (external clock is much slower)

The clock I'm externally using has fixed frequency, so can't be multiplied unfortunately. Is it true that this digitizer can't accept a clock lower than 400MHz? Is it due to any LPF circuitry inside the digitizer?

Also the clock ranges from 0.1V to 0.8V (700 mVpk-pk), which is a bit less than the input voltage range in the specification..

Thanks.

07-03-2013 04:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Kellerman,

It is true that the digitizer cannot accept a clock lower than 400MHz because there is other digital circuitry in the FAM (FlexRIO Adapter Module) that needs to run off that clock. As far as the voltage range of your input clock, it is not guaranteed to work at that range, as the minimum spec is 800mVpk-pk. Although the spec says 800mVpk-pk, it is possible that it works at 700mVpk-pk if it is between 400 and 800 MHz.

Regards,

Chris

Applications Engineer

01-07-2014 09:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

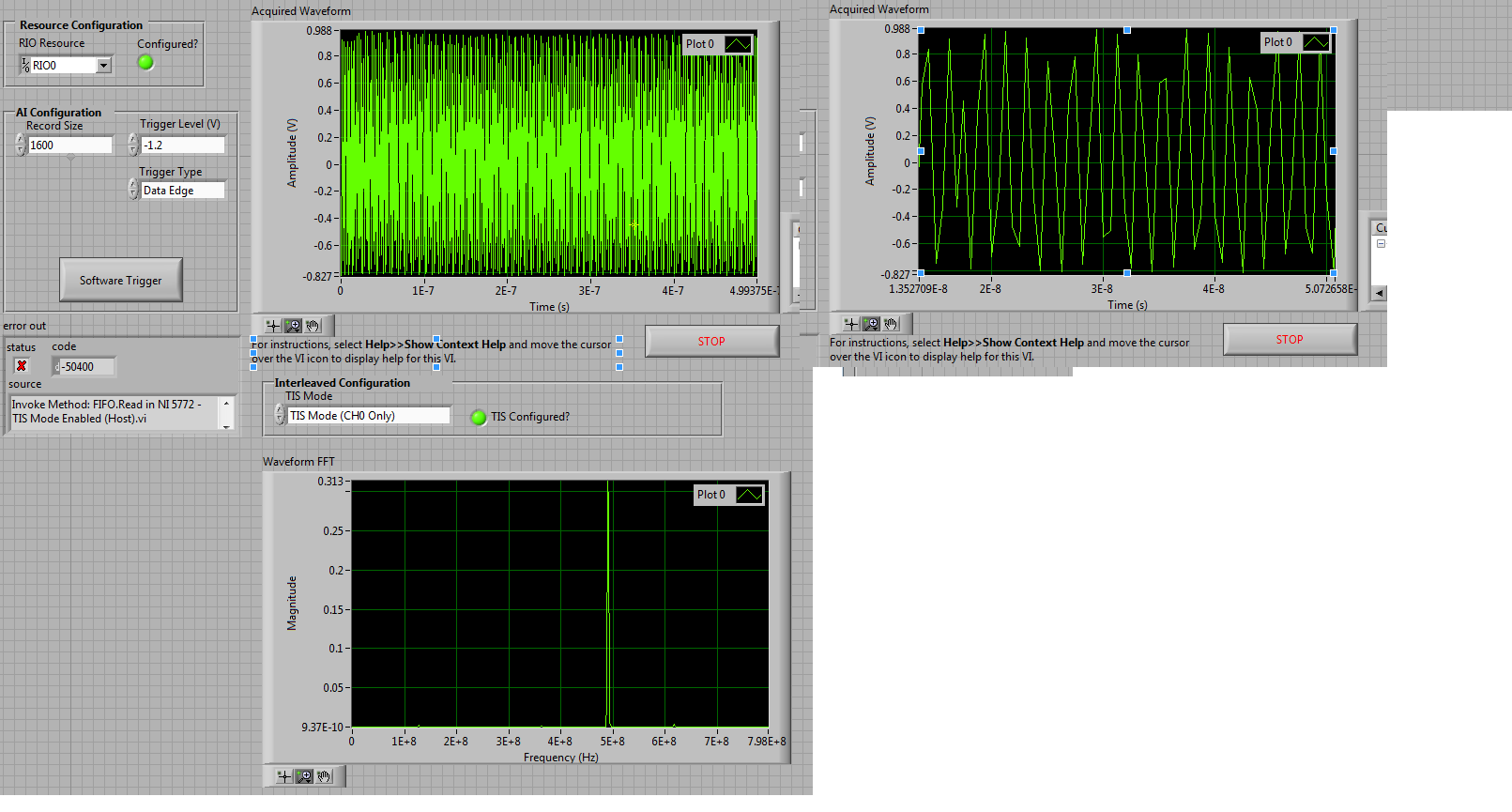

We are trying to use the NI 5772 with an external clock. The following is a screenshot of when we plug in the external clock to the AI 0 line of the NI 5772 using the TIS mode enabled to sample at 1.6 GHz. On the right is a screenshot of the acquired waveform zoomed in to show the peaks Also, I have calculated the FFT at the bottom.

When we plug the external clock source into the CLK_IN lline, and use the NI 5772 - Clock Select example, and select externa clock, however, it will hang at the Configure Clock subVI. Selecting an internal clocks will work. I have probed the first loop in Configure Clock when it waits for 'User Command Idle' to go to true, and it never does. The comments note that the loop can hang if the externa clock is not corret, but given the requirements fo the external clock (a frequency range of 400-800 MHz, a voltage range of 800 mV pp), I cannot understand why it would not like the external clock input

01-08-2014 03:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your clock signal isn't < 800mVpp, it actually looks like its around 1.64Vpp. Your applying too much voltage to the unit.

SISU

01-08-2014 03:50 PM - edited 01-08-2014 03:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The manual claims the pp voltage has to be in the range 800 mV - 4 V.

http://www.ni.com/pdf/manuals/373625a.pdf

We are actually using an RF amplifier in the loop, because our raw signal only has a pp of 150 mV. It doesn't work with a signal level of +/-150 mV, either.

01-09-2014 07:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Patrick,

I don't think the amplitude or frequency (500MHz it looks like) are an issue, they both appear in spec. The code seems to dead end at the FPGA timed loop clock configuration source; that's where the external clock is going and it is there that the vailidity of the clock would be determined. Have you made sure to meet the other specs, such as impedance matching to 50 ohms? Any other details you can provide about the clock signal would be helpful as well. Make sure the cable connections are tight as well, due to the sensitivity to noise at these higher frequencies.

01-15-2014 07:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes the output impedance of the amplifer is designed 50 ohms, so that is not an issue ...

We have hooked it up to a function generator, and gotten it to work at 500 MHz even at the lower voltages.

After unplugging the function generator, then plugging in our external clock, it will run, by the signal is corrupted at several points.

The long period duty cycle of the clock is only about 60% (i.e. there is a log period where no clock signal is sent)

I think the issue may also have to do with the clock phase, which is not unform. The NI 5772 uses a Texas Instruments ADC . Reading the manual for tha part, it seems like the clock requirements are pretty tight, as it is expecting a very low jitter clock signal

Another group we work with has a digitizer made by another company that apparently solves this issue by routing the clock though a VCO, which somehow stablizes the clock. However, after some consultation we are not convinced that is the real solution either, because the clock is supposed to be somewhat unstable in the first place, which is the issue we are trying to correct for (we are trying to avoid having to resample the data in software)

01-17-2014 10:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Patrick,

We've discussed this and it indeed looks like an issue with the sensitivity of the ADC clock requirements. One idea is to read in both your signal and external clock, sampling with an internal clock, and then in software go through and only take the data points that correspond to rising edges of the external clock.

The VCO is hard to be sure about, since as you mentioned the clock you're using is somewhat unstable and the goal of the VCO would be to make it more stable, you might be sampling at the wrong time with respect to the original external clock.

I would see about importing both the external clock and signal on the FPGA side and seeing if you can measure the samples on the external clock edges; it doesn't look like there's any other way to do this in hardware with the 5772.