- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

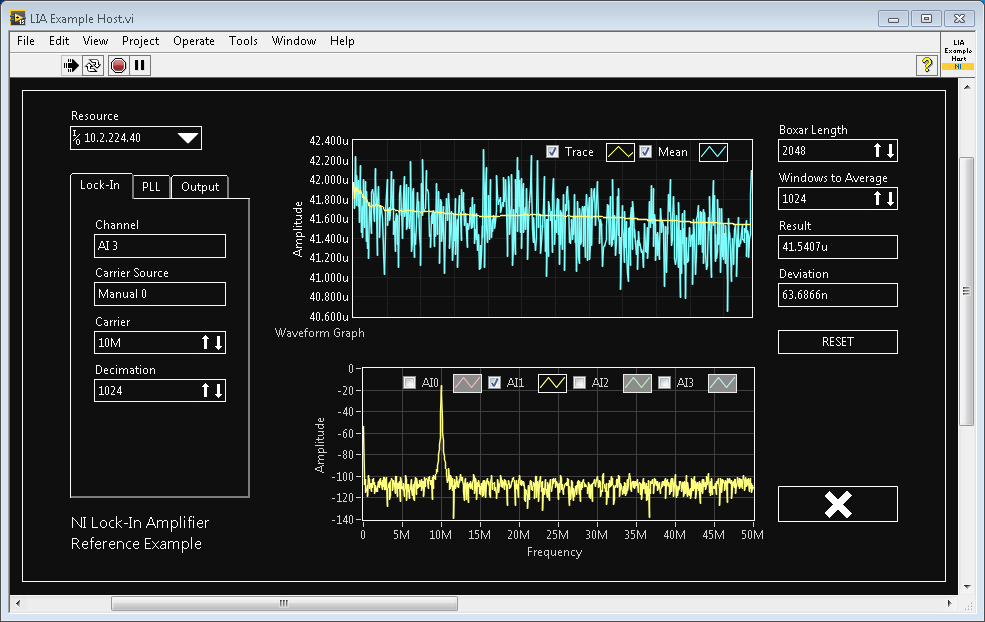

The NI Lock-In Amplifier Reference Example package provides FPGA, Real-Time, and Host example code that implements a lock-in amplifier on NI FlexRIO targets. A lock-in amplifier extracts a signal with a known carrier wave from a noisy environment through phase-sensitive detction. For a more detailed description, visit the Wikipedia page.

This example instantiates 4 FPGA-based lock-in amplifiers using the NI 5783 FlexRIO Adapter Module. Each 16-bit, 100 MSPS lock-in path provides 40 MHz of bandwidth. Additionally, 4 16-bit, 200 MSPS analog output channels provide precise reference tones. Two of the lock-in amplifier analog inputs may be repurposed as PLLs for external reference signals.

Latest Version

NI Lock-In Amplifier Reference Example 1.0.0.7

Software Requirements

LabVIEW 2015 and

LabVIEW 2015 FPGA Module and

NI-FlexRIO 15.5

Hardware Requirements

PXIe-7976R + 5783 FlexRIO Adapter Module or

NI 7935R + 5783 FlexRIO Adapter Module

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi,

I am Shigeru Minami from NI Japan.

I have some questions about this LIA reference example.

Please let me know the details.

1. I guess that this LIA reference example is for "single phase" lock in amplifier.

Because I can get only amplitude, but not phase.

However, this example has 8 DMA resources for "I" x 4ch and "Q" x 4ch.

In the near future, do you have a plan to modify this example to "dual phase" lock in amplifier?

If it is easy, I want to modify it.

Please advise me.

2. This example is for NI 5783.

And, I want higher sampling rate, for example 250MS/s or more.

If possible, I choose some high speed FlexRIO adapter modules, NI 5782: 250MS/s 2AIs or NI 5761: 250MS/s 4AIs.

So, I tried to use this sample with NI 5782.

As result, this sample works fine under 125MS/s sampling rate: Multi-Sample CLIP.

However, under 250MS/s sampling rate: Single-Sample CLIP, can not compile FPGA code.

I guess that PLL (Hilbert).vi is huge for 250MS/s because of timing violation information.

Is it possible to modify this example for 250MS/s or more sampling rate?

3. In the near future, do you have a plan to support Reconfigurable Oscilloscopes, for example, PXIe-5171R?

Almost FlexRIO adapter modules has single and narrow range of voltage.

However, PXIe-5171R has some ranges, some customers want to use it.

4. What is "Result"?

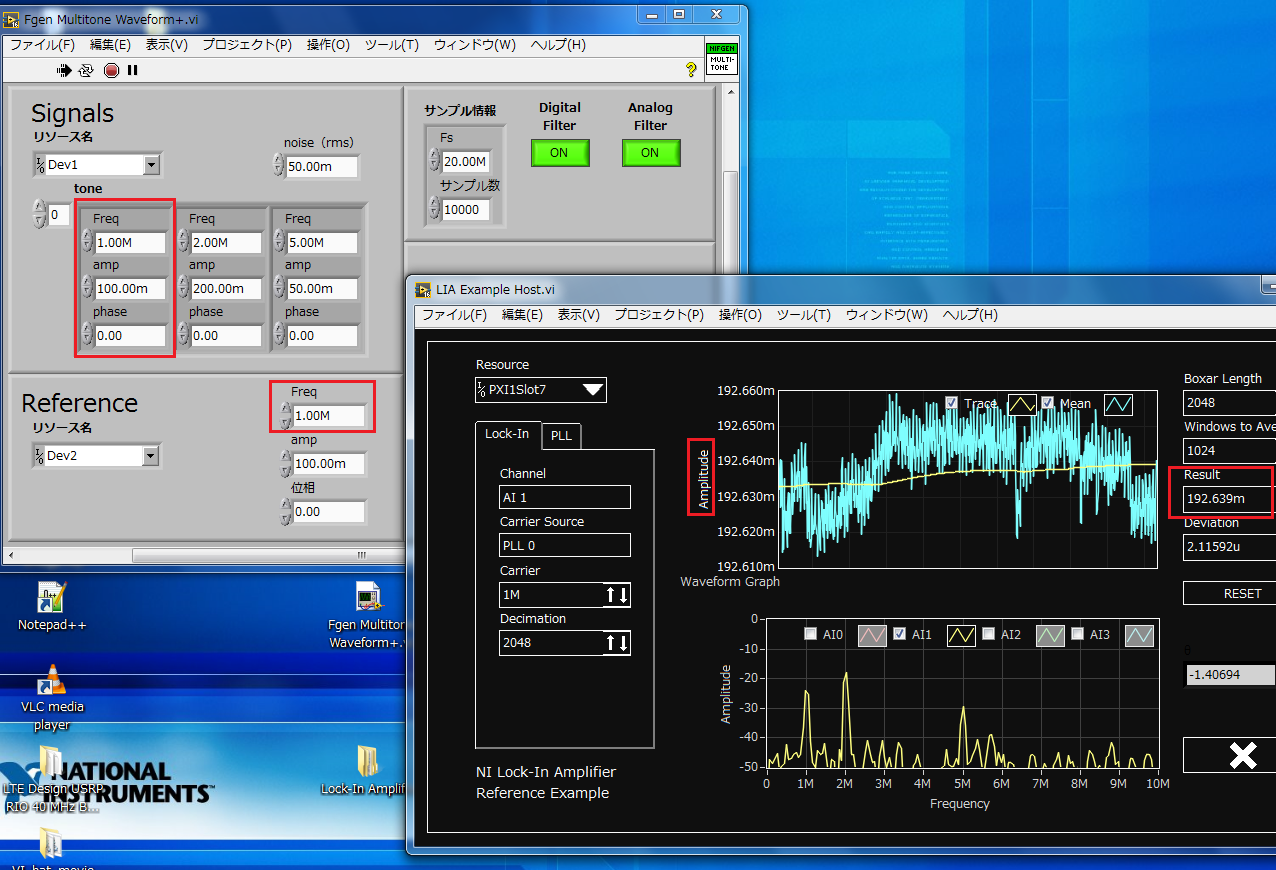

With 2 FGEN boards and TClk synchronization program, outputs 2 signals: measurement signal and reference signal.

Please see the following images.

<Lock-in 1MHz and 100mV signal.>

Result is 192mV.

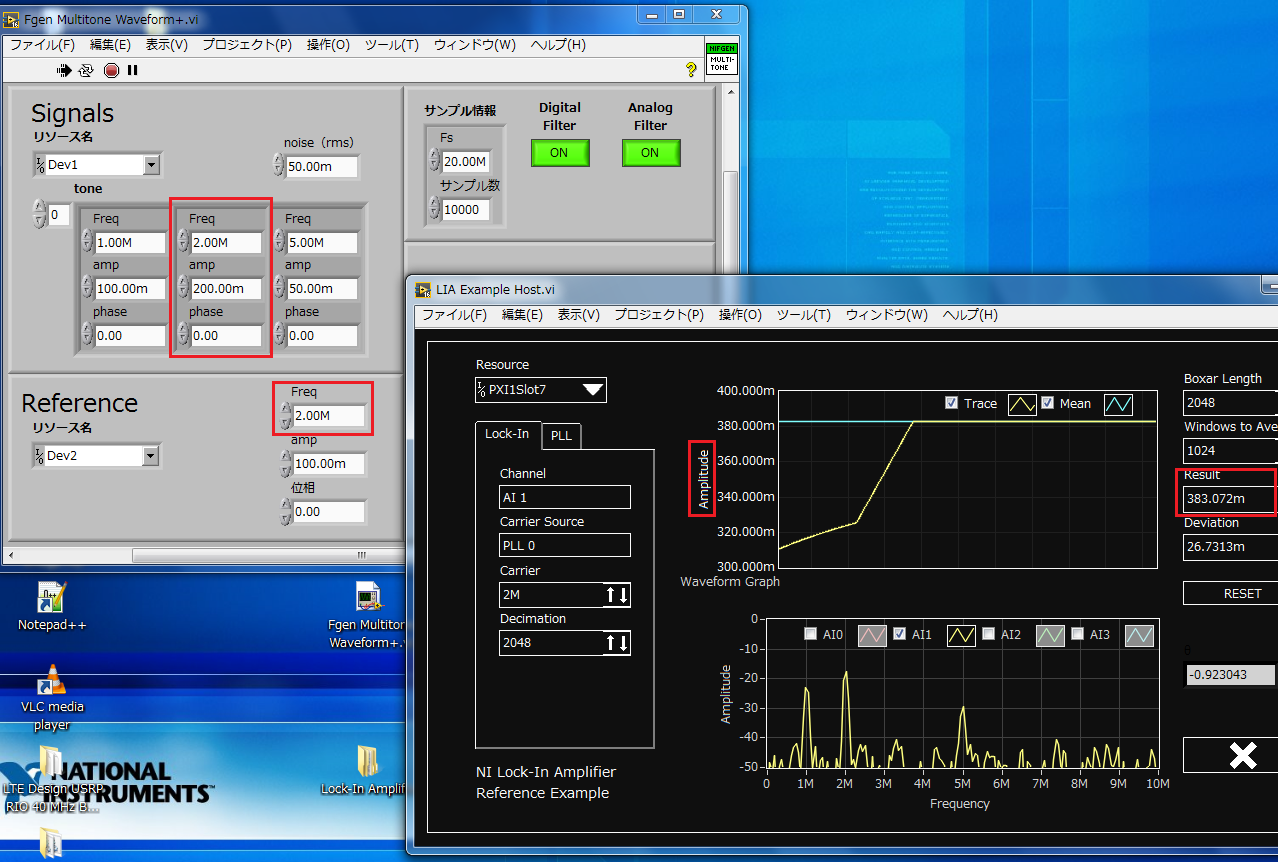

<Lock-in 2MHz and 200mV signal.>

Result is 383mV.

<Lock-in 5MHz and 50mV signal.>

Result is 96mV.

At first, I think that this issue is linked to the following KB.

http://digital.ni.com/public.nsf/allkb/E6FCA8226A164202862572110046E717?OpenDocument

However, input impedance of NI 5782 and NI 5783 is 50 ohm.

Of course, output impedance of NI 5442 is 50 ohm.

So, I have no idea.

Why does amplitude twice?

Is "Result" Voltage peak to peak?

Please let me know.

Thank you for your time and help,

Regards,

Shigeru Minami

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello,

I have been trying to access this reference example without success.

Is it still available?

Best regards,