Comparing FPGA resource usage of bool vs enum

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Code and Documents

Attachment

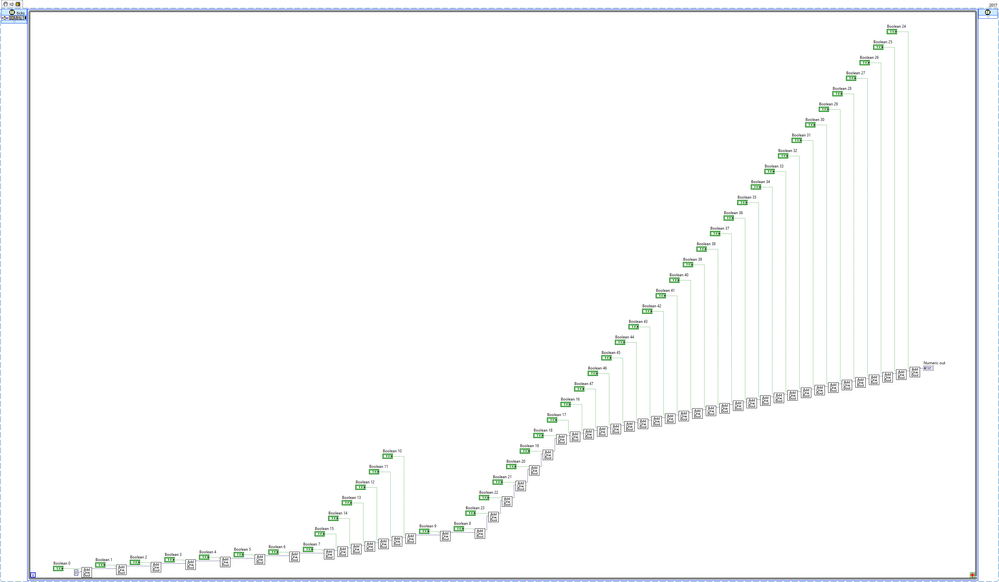

I wanted to measure what was the performance hit if any between using an enum selector vs a bool selector. Here's the top level code using booleans. The subVI will add one to the bottom input if the boolean is true. The overall effect is that the code will very quickly count how many of the top inputs are true

Here's the compilations results using LV2017, SbRIO Vivado target, cloud compile service:

Compilation completed successfully.

Device Utilization

---------------------------

Total Slices: 25.3% (3359 out of 13300)

Slice Registers: 8.7% (9225 out of 106400)

Slice LUTs: 17.8% (9457 out of 53200)

Block RAMs: 5.0% (7 out of 140)

DSP48s: 0.0% (0 out of 220)

Timing

---------------------------

80MHz: 80.00 MHz (Met MHz maximum)

40 MHz Onboard Clock: 40.00 MHz (Met MHz maximum)

Compilation Time

---------------------------

Date submitted: 9/5/2017 11:44 AM

Date results were retrieved: 9/5/2017 11:51 AM

Time waiting in queue: 00:14

Time compiling: 06:57

- Generate Xilinx IP: 00:00

- Synthesize - Vivado: 02:12

- Optimize Logic: 00:16

- Place: 00:59

- Optimize Timing: 00:13

- Route: 01:08

- Generate Programming File: 00:42

- Finalize Programming File: 00:00

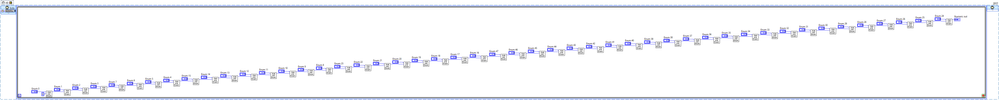

And then, here's the same code but using an enum with two possible values (Leave alone, add one).

LabVIEW FPGA: The compilation failed due to timing violations.

Click the Investigate Timing Violation button to display the Timing Violation Analysis window.

Device Utilization

---------------------------

Total Slices: 26.2% (3479 out of 13300)

Slice Registers: 9.4% (9989 out of 106400)

Slice LUTs: 18.8% (10010 out of 53200)

Block RAMs: 5.0% (7 out of 140)

DSP48s: 0.0% (0 out of 220)

Timing

---------------------------

80MHz: 79.03 MHz

40 MHz Onboard Clock: 40.00 MHz (Met MHz maximum)

Compilation Time

---------------------------

Date submitted: 9/7/2017 12:08 PM

Date results were retrieved: 9/7/2017 12:16 PM

Time waiting in queue: 00:14

Time compiling: 07:25

- Generate Xilinx IP: 00:00

- Synthesize - Vivado: 02:18

- Optimize Logic: 00:16

- Place: 01:10

- Optimize Timing: 00:14

- Route: 01:19

- Generate Programming File: 00:43

- Finalize Programming File: 00:00

To try and have the best of both worlds (lower delay time, lower usage, and highly descriptive enums), I created this idea on the exchange

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

The differences in Register usage are largely due to the larger FP controls.

The increase in LUT however is linked to the extra mux operations required at the output of the Case Structure. I'm assuming the bit width of the data leaving the Case structure is ewqual in both test scenarios? If so then the LUT usage requires approx. 12 LUTs more per instance than the dual-boolean version. Things like this add up.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thanks for the breakdown of the use. I wanted to make sure that LV didn't already optimize the data size of the enum for the front panel control registers and the case structure sectors and outputs before I proposed the idea to make the optimization or allow the user to make that optimization.

I just realized I messed up on the datatype for the total. I'll fix it.