cRIO Reference Trigger on FPGA with Data Streaming to Real-Time

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW FPGA Module

- LabVIEW Real-Time Module

- LabVIEW

Software

Code and Documents

Attachment

Overview

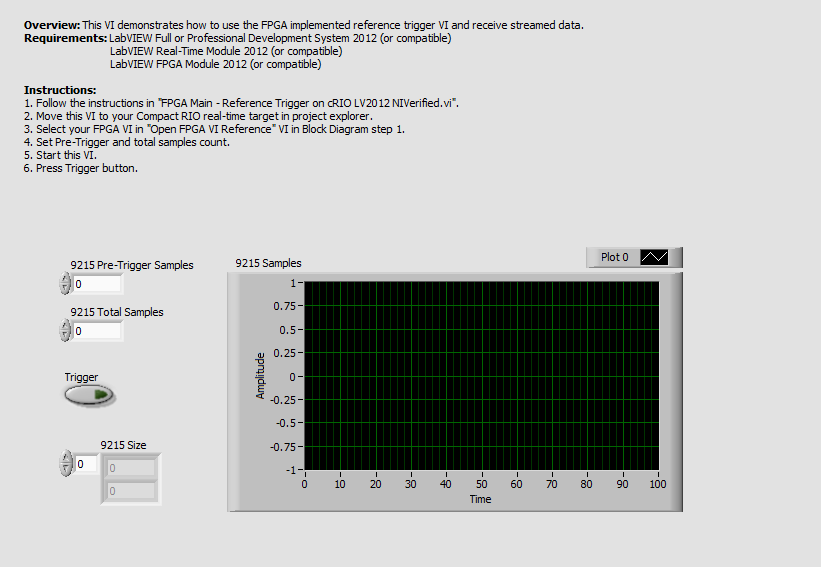

This example demonstrates how to implement a reference trigger on FPGA and stream trigger data to Real-Time application.

Description

Requirements

Software

- LabVIEW Full or Professional Development System 2012 (or compatible)

- LabVIEW Real-Time Module 2012 (or compatible)

- LabVIEW FPGA Module 2012 (or compatible)

Hardware

- Compact RIO FPGA and Real-Time target (e.g. cRIO 9024 or compatible)

- Analog Input C Series Module (e.g. NI 9215 or compatible)

Steps to Implement or Execute Code

- Download and extract the attached file "Reference Trigger on cRIO LV2012 NIVerified.zip".

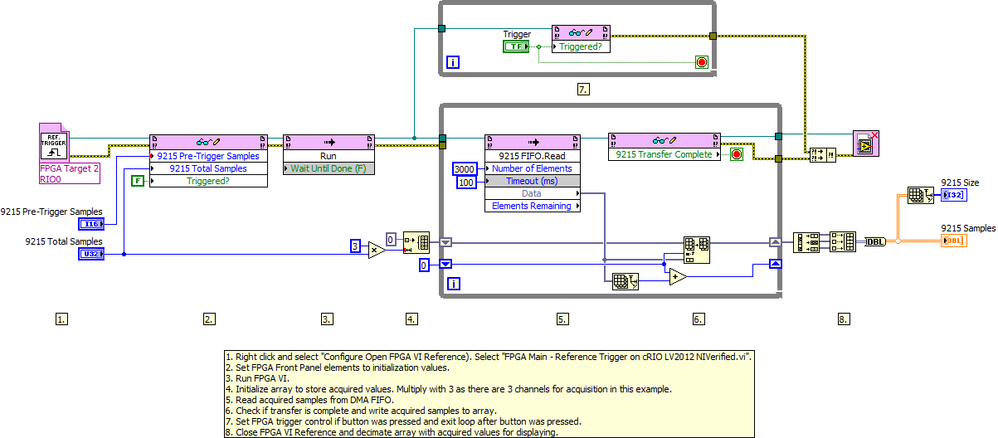

- Follow the instructions in Real-Time and FPGA Front Panel and Block Diagram and run the program.

Additional Information or References

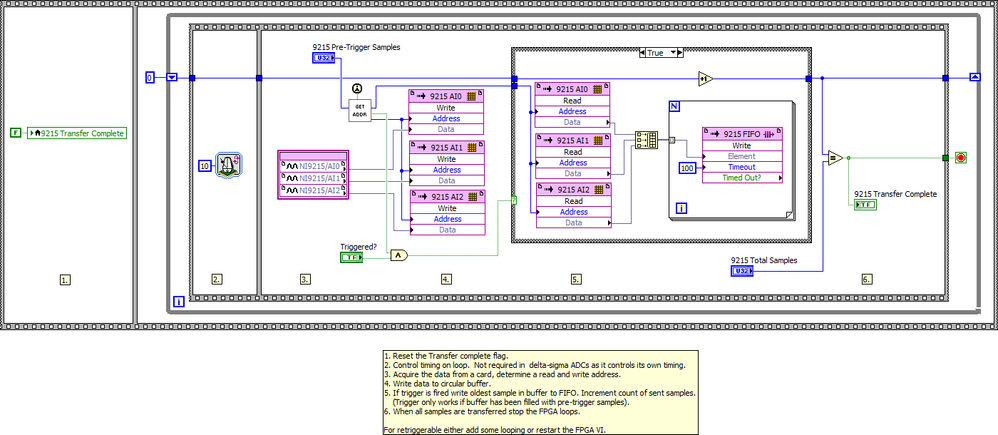

FPGA VI:

Write data into a circular buffer with a subVI generating the write addresses. When the trigger fires the subVI also generates the address for the oldest item in the buffer. Once all the requested samples have been written to the FIFO the FPGA flags to the RT and stops executing. To make this retriggerable simply loop!

We are generating the trigger from RT for testing but this could come from analog values on the channels or another part of the FPGA code.

Real-Time VI:

========

Ask me about Rust & NI Hardware

My writings are at https://www.wiresmithtech.com/devs/

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi James

I am trying to develop this myself but I dont know where to start. I dont like the idea of buffering into block memory as i dont want to limit the amount of post-trigger values from the FPGA to the host. I would rather set a predefined pre-trigger buffer length (say 5000 samples) and stream that to the host along with post-trigger samples.

I see that there is a bug in the first screen shot, i.e. the image is not showing the FPGA implementation. are you able to email me the details if you dont mind.

my email address is ronny.veljanovski@live.com.au

Looking forward to your reply.

Ronny

Project Manager

Monash Node of CRCBID Ltd

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi James

Thanks for the quick response. The concept is very streamlined and cool.

I will work on it tomorrow and see if it works once I make some changes to my VI's.

Thanks again

Ronny

From: JamesMcN <web.community@ni.com<mailto:web.community@ni.com>>

Reply-To: "ni-2144636708-170q-2u-bm4@decibel.ni.com<mailto:ni-2144636708-170q-2u-bm4@decibel.ni.com>" <ni-2144636708-170q-2u-bm4@decibel.ni.com<mailto:ni-2144636708-170q-2u-bm4@decibel.ni.com>>

Date: Thu, 10 Mar 2011 21:07:27 +1100

To: Ronny <ronny.veljanovski@crcbid.com.au<mailto:ronny.veljanovski@crcbid.com.au>>

Subject: - Reference Triggers on FPGA (With Data Streaming)

Community<http://decibel.ni.com/content/index.jspa>

Reference Triggers on FPGA (With Data Streaming)

modified by JamesMcN<http://decibel.ni.com/content/people/JamesMcN> in NI Developer Community - View the full document<http://decibel.ni.com/content/docs/DOC-15052

Project Manager

Monash Node of CRCBID Ltd

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi,

I was wondering why you had decided to use a separate block memory for each Analog Input. Is it possible to have one block memory and interleaved data from each into this? Thanks!