Verilog Waveform Generator (String Manipulation) using LabVIEW

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW

Software

Code and Documents

Attachment

Overview

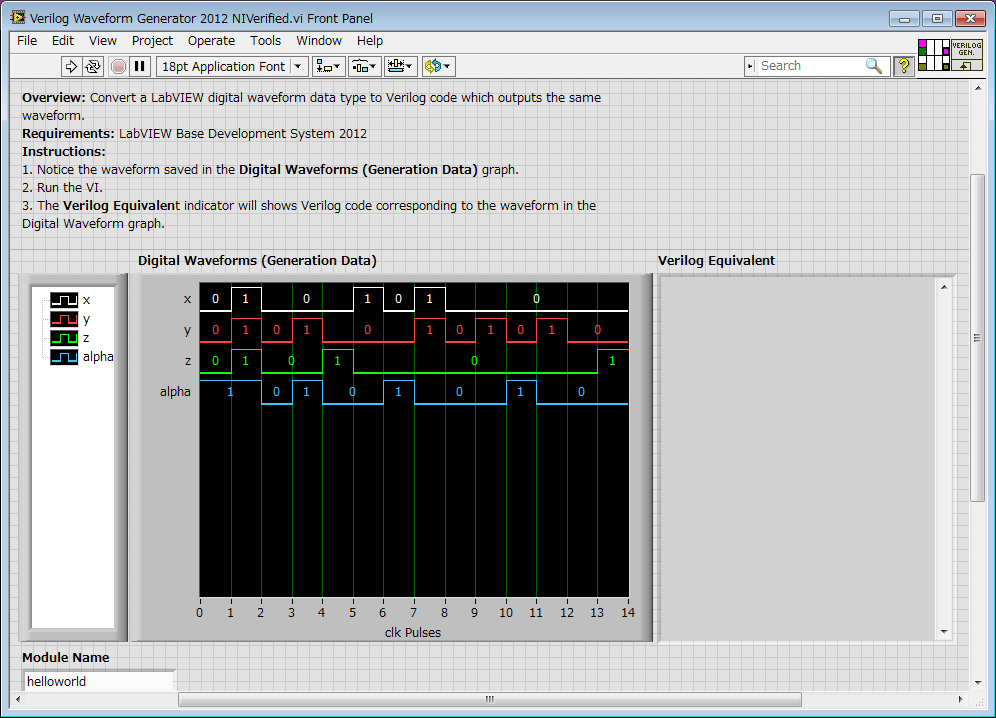

Convert a LabVIEW digital waveform data type to Verilog code which outputs the same waveform.

Description

When programming FPGAs with Hardware Description Languages (HDLs) such as VHDL and Verilog, a very common task that needs to be performed is the generation of control signals for separate code modules within the FPGA or for external peripheral devices such as Liquid Crystal Displays (LCDs). Often, the task of ordering and triggering of these control signals in these low-level languages can be pretty arduous, and often results in the programmer consuming a lot of coffee, which can sometimes be unhealthy.

LabVIEW's Front Panels offer the Digital Waveform Graph, a great way to visualize and manipulate digital data. We can use the graph to first prototype our generation signals and then use Property Nodes and String Manipulation to generate the equivalent Verilog code.

The Verilog code produced assumes the incorporation of a Clock Signal (clk) and a Reset Signal (rst). The Clock Signal will need to run at least twice the rate of the maximum frequency of any signal depicted in the Waveform Graph.

Requirements

- LabVIEW Base Development System 2012 (or compatible)

Steps to Implement or Execute Code

- Open “Verilog Waveform Generator 2012 NIVerified.vi”

- Notice the waveform saved in the Digital Waveform graph.

- Run the VI.

- The “Verilog Equivalent” indicator will shows Verilog code corresponding to the waveform in the Digital Waveform graph.

Additional Information or References

VI Front Panel

**This document has been updated to meet the current required format for the NI Code Exchange.**

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Nice, thanks.

PS. the picture made me write the comment.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thanks very much!