NI LabVIEW RIO Evaluation Kit - Additional Examples

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW RIO Evaluation Kit

Other

Code and Documents

Attachment

Description

Description-Separate-1Overview

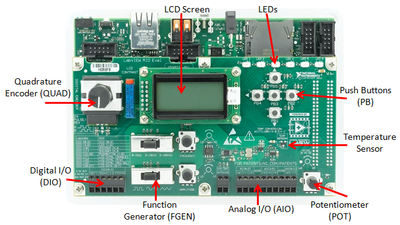

The following examples are designed for the NI LabVIEW RIO Evaluation Kit. The examples demonstrate some of the embedded system design capabilities of the LabVIEW FPGA Module and LabVIEW Real-Time Module running basic examples on the kit.

Description

The LabVIEW code for the following examples can be downloaded all at once, using the zip file below. For additional help with each example, see the documentation included in the application. For more exercises, visit the LabVIEW RIO Evaluation Kit Community.Steps to Implement or Execute Code

1. Event Counter, Falling Edge

This VI contains an event counter that increments on every falling edge of the input trigger signal (PB1). To reset the value of the counter, use the designated asynchronous reset button (PB2) on the board.

1 - Event Ctr, Falling Edge.zip

Instructions:

- From the download directory, open Event Ctr, Falling Edge - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run Event Ctr, Falling Edge.vi.

2. Event Counter, Programmable Edge

This VI contains an event counter that increments on the hardware selected edge of the input signal, either rising or falling. To reset the value of the counter, use the designated reset button (PB2) on the board.

2 - Event Ctr, Programmable Edge.zip

Instructions:

- From the download directory, open Event Ctr, Programmable Edge - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run Event Ctr, Programmable Edge.vi.

3. Quadrature Counter

This VI uses the quadrature encoder hardware on the evaluation board daughter card to count pulses on the encoder. The VI decodes the A and B pulses and an 8-bit count, displays it on the Front Panel as well as in binary on the evaluation board LEDs,and shows the current count position of the encoder. Use the reset button on the VI front panel to reinitialize the quadrature encoder count to zero.

3 - Quad Ctr.zip

Instructions:

- From the download directory, open Quad Ctr – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run Quad Ctr.vi.

4. Quadrature Counter, Index Save

This VI interprets a quadrature encoder input using the A and B signals and also asynchronously saves the current position value on every valid index state. This means that the position value is stored each time a particular configuration of inputs is seen. In this case, a valid index state is defined when Line A, Line B, and Input Z are all low.

4 - Quad Ctr, Index Save.zip

Instructions:

- From the download directory, open Quad Ctr, Index Save - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run Quad Ctr, Index Save.vi.

5. Two Edge Measurement

This VI performs a two edge separation measurement between the push buttons PB1 and PB2. The output is the difference in milliseconds between rising edges of PB1 and PB2.

5 - Two Edge Measurement.zip

Instructions:

- From the download directory, open TwoEdge – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run TwoEdge.vi.

6. PWM Generation

This VI generates a pulse width modulated output with variable high and low periods. The program uses the potentiometer to vary the duty cycle from 0% to 100%. In addition, use the onboard Function Generator frequency toggle switch to select between .5 Hz and 100 Hz PWM frequencies. The result of the PWM is represented on the LEDs.

6 - PWM Generation.zip

Instructions:

- From the download directory, open PWM Out – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run PWM Out.vi.

7. PWM Generation and Measure – Simple

This VI is divided into two parts - PWM generation and PWM measurement. First, it generates a pulse train on a digital output according to low and high period controls. Next, it measures the same digital signal using a digital input and measures the high and low periods in software.

7 - PWM Generation and Measure - Simple.zip

Instructions:

- From the download directory, open PWM Simple Generation and Measure – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Physically wire DIO0 to DIO1 on your eval board.

- Open and run PWM.vi.

8. PWM Generation and Measure – Latched

This VI is divided into two parts - PWM generation and PWM measurement. It first generates a pulse train on a digital output according to low and high period controls. Changes to these control values take place one full period following the assertion of the Load control. It then measures the same digital signal using a digital input to evaluate the high and low periods in software. The high and low period measurements are updated after the Latch control is asserted.

8 - PWM Generation and Measure - Latched.zip

Instructions:

- From the download directory, open PWM Latched Generation and Measure - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run PWM Latched.vi.

9. Look-up Table

This VI demonstrates the functionality of a look-up table (LUT) using the eval kit hardware. It references a predefined table of values corresponding to a sine waveform. Then, it outputs the waveform on the six LEDs of the evaluation kit daughter board. The program uses the potentiometer on the daughter card to vary the frequency.

9 - Look-up Table.zip

Instructions:

- From the download directory, open LUT - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run Sin LUT.vi

10. Butterworth Filter

This application demonstrates the use of the Butterworth filter on the FPGA as well as FPGA to real-time processor communication. The FPGA generates a noisy sine wave and passes the waveform through an analog output. By using a loopback connection, the program reads the waveform back through an analog input and filters out the noise. The FPGA sends waveform data to the processor where it is formatted to display on a chart.

10 - Butterworth Filter.zip

Instructions:

- From the download directory, open Butterworth Filter - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and examine the FPGA personality defined by Generation and Filter (FPGA).vi.

- Physically wire Analog Output 0 (AO0) to Analog Input 0 (AI0) on your eval board.

- Open and run Host.vi on the real-time processor.

11. Watchdog Personality

This VI creates an FPGA personality to emulate a hardware watchdog. If the watchdog timer is not reset prior to a software-defined expiration time (in milliseconds), an expiration indicator will show that the watchdog has timed out.

11 - Watchdog Personality.zip

Instructions:

- From the download directory, open WD Polling – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and run WD Polling.vi.

12. Watchdog Interrupt

This application builds off of the FPGA personality created in the previous example. If the watchdog timer is not reset prior to a software-defined expiration time (in milliseconds), an expiration indicator will show that a timeout has occurred. This will trigger the real-time VI to display a dialog box on your user interface indicating the watchdog expired. This shows how the watchdog can be used to trigger interrupt code.

12 - Watchdog Interrupt.zip

Instructions:

- From the download directory, open WD Occurrence – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and examine WD Polling.vi on the FPGA target.

- Open and run the Watchdog Occurence.vi.

13. Real-Time FIFO

This application demonstrates the use of a Real-Time FIFO to deterministically communicate data between two loops running on the real-time processor. The first FIFO in this example contains control information while the second contains waveform data for display. A low priority loop reads waveform data and displays it on a graph while writing data to the control FIFO. A high priority loop writes waveform data to the data FIFO and regulates the waveform according to data on the control FIFO.

13 - RT FIFO.zip

Instructions:

- From the download directory, open RT FIFO Communication – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target.

- Open and run RT FIFO.vi.

14. TCP Client and Server

This application shows how to use TCP communication to transfer streaming data from a Real-Time target to a host computer. A TCP connection is opened between the targets. The data server on the Real-Time target generates waveform data and transfers it to the data client on the computer.

14 - TCP Client and Server.zip

Instructions:

- From the download directory, open TCP Comm – sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target.

- Open and run the Simple Data Server.vi on the eval kit target. It will wait up to 60 seconds for a connection from the computer on the specified port.

- Open and run the Simple Data Client.vi from under the My Computer target.

- Make changes on Simple Data Server.vi to be reflected on the Simple Data Client.vi data plot.

15. TCP File Transfer

This application illustrates a TCP file transfer. An FPGA VI generates sine waveform data. The real-time processor reads a finite number of points from this FPGA- generated waveform and writes the data to a spreadsheet file on the target. The file is transmitted via TCP from the eval kit target to your host computer, which then reads the spreadsheet file and outputs the waveform to a front panel graph.

15 - TCP File Transfer.zip

Instructions:

- From the download directory, open TCP File Transfer - sbRIO.lvproj.

- Expand the directory for the LabVIEW RIO Evaluation Kit target, then the FPGA target.

- Open and examine FPGA Personality.vi on the FPGA target.

- Open and run TCP File Receiver.vi on your computer. It will wait up to 60 seconds for a connection from the Real-Time target on the specified port.

- Open and run TCP File Sender.vi on the Real-Time target.

- View the waveform results on the graph contained in TCP File Receiver.vi.

- Alternatively, you can log into your target and read the unformatted file in a browser. Check the front panel of TCP File Sender.vi for instructions.

Download Additional Examples.zip below to get all of the examples found on this page in one zip file.

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi cpeacock,

Could you please upload the examples from the tutorial as well? I have a board with me and am quite new to Labview and would like to work through this tutorial: ni_labview_rio_eval_tutorial.pdf

I have not found the DVD with the board but would like to do the examples.

Also, I could not find a way to message you privately.

Regards,

Nandor