Generate pulse train in LabVIEW FPGA

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW FPGA Module

- LabVIEW

Software

Code and Documents

Attachment

Overview

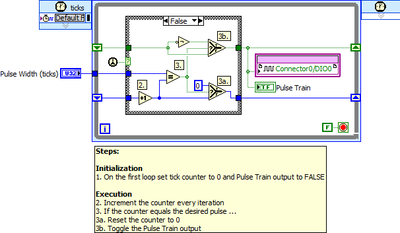

The example demonstrates how to implement a pulse train on a FPGA.

Description

The example demonstrates how to implement a pulse train on a FPGA. The example is configured to run on a R-series FPGA hardware but can be easily use with any NI FPGA hardware with digital outputs available.

The example makes use of a Single-Cycle Timed Loop (SCTL) to increase maximum pulse train frequency and to reduce FPGA resource usage.

Requirements

Software

- LabVIEW 2012 Base Development System (or compatible)

- LabVIEW 2012 FPGA Module (or compatible)

Hardware

- No hardware is necessary to use this example VI in simulation mode

- To run this example on real hardware you need any LabVIEW FPGA Module compatible hardware with at least one digital output available

Steps to Implement or Execute Code

- Open the attached file

- Configure the pulse width

- Run the VI

Additional Information or References

**The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text 'NIVerified'. Read here for more information about the new Example Guidelines and Community Platform.**

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.