FPGA - Pulse Train Generation Using LabVIEW

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- CompactRIO|SingleBoardRIO

Hardware

- LabVIEW FPGA Module

- LabVIEW Real-Time Module

- LabVIEW

Software

- NI RIO

Driver

Code and Documents

Attachment

Overview

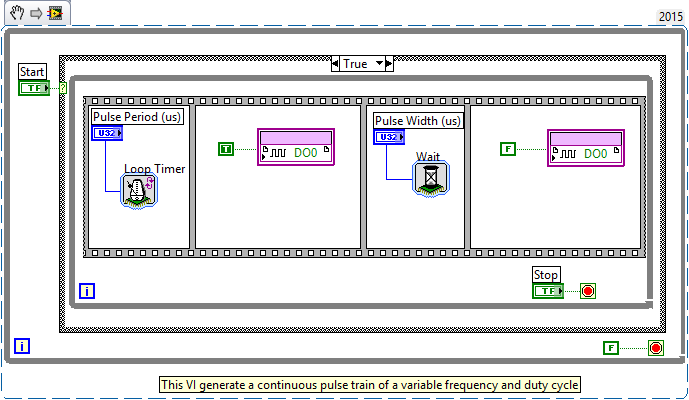

This example uses LabVIEW FPGA to generate a continuous pulse train of a variable frequency and duty cycle. The pulse train is generated on the FPGA and is output from a cRIO digital output module.

Description

Pulse train A repetitive series of pulses, separated in time by a fixed and often constant interval. The duration of each pulse and its duty cycle are also often made constant. In this example we are generating a digital continuous pulse train of a variable frequency and duty cycle. The pulse train is generated on the FPGA and is output from a cRIO digital output module.

Requirements

LabVIEW 2015 or compatible

LabVIEW 2015 FPGA or compatible

LabVIEW 2015 RT or compatible

NI RIO driver

Steps to Implement or Execute Code

- Open the cRIO Pulse Train Generation LV2015 NI Verified Project

- Configure the CRIO IP and connect

- Compile cRIO Pulse Gen (FPGA) VI

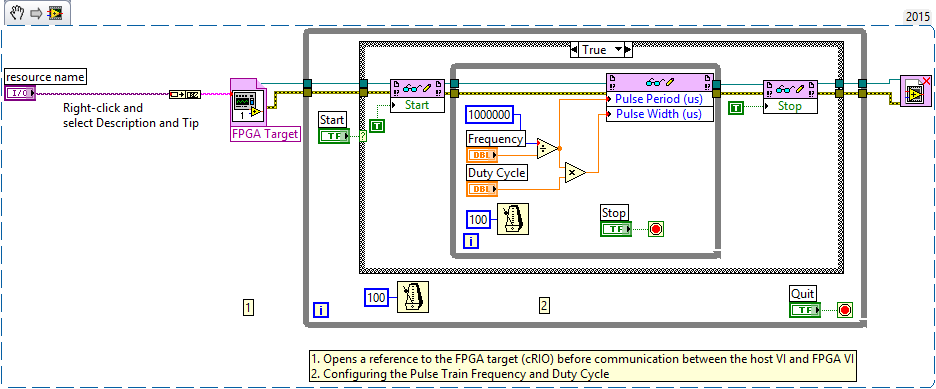

In the cRIO Pulse Gen (Host) VI

- Provide the compiled FPGA VI bit file in the Open FPGA VI Reference function in the block diagram

- Enter Resource Name, Frequency and Duty Cycle

- Run the VI

Additional Information or References

cRIO Pulse Gen (HOST) VI Block Diagram

cRIO Pulse Gen (FPGA) VI Block Diagram

**This document has been updated to meet the current required format for the NI Code Exchange. **

Regards,

Dan King

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.