- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

sbRIO9651 power supply design

11-13-2014 03:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

We have designed a sbRIO carrier board for sbRIO-9651.We are not using any banks and given the same volatge to all banks 3.3V from the same rail that i given to the main supply of sbRIO.

If i am not using the banks what will be the maximum power consumption of banks.

Is there any problem that i use a single regulator for sbRIO main and all 3 banks ?

i have designed a single powersupply with 3.3V@3A.Is it sufficient for my case ?

11-13-2014 02:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi manumohan.mm,

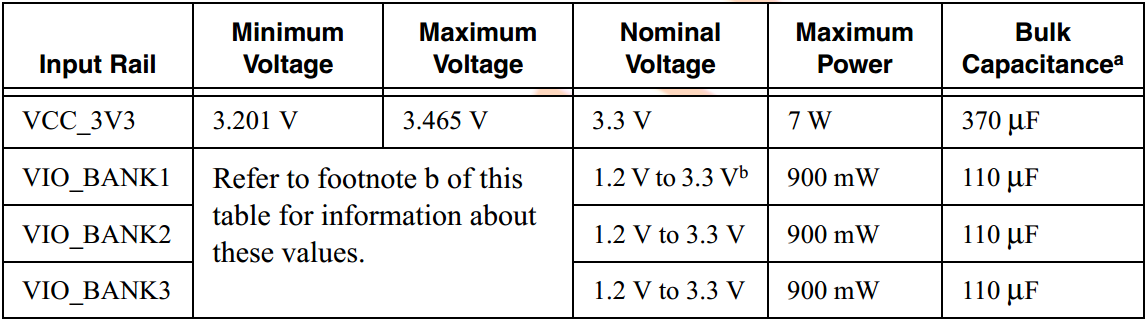

The VCC_3V3 rail requires an absolute maximum of 7W. This power consumption is highly dependent upon how much FPGA fabric is being consumed, how fast it is being toggled, and the processor utilization. If you are not using VIO_BANK1, VIO_BANK2, or VIO_BANK3, those still must be powered. The easiest way to power the unused banks are to use the supply that is powering your VCC_3V3 rail. A separate supply is not required to power the unused banks or even banks that are being used and operated at 3.3V.

Since you are not using any of the DIO on those banks, there will be no power consumption on those banks.

Your 3.3V @ 3A power supply will give you close to 10W which will cover the VCC_3V3 power requirements with margin to spare. We expect most applications to consume 3-5 W from the VCC_3V3 rail but of course it is highly dependent on the application. If the same 3.3V power supply is also powering your carrier board electronics, you have to verify that the power consumption of the sbRIO-9651 SOM plus your carrier board and any other loads do not exceed your power supply design's maximum limits. I hope this answers your question but please let me know if you have further questions regarding this topic.

National Instruments