Inactive

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

VeriStand : Allow PWM out frequency update while running for FPGA pesonnality

Hello,

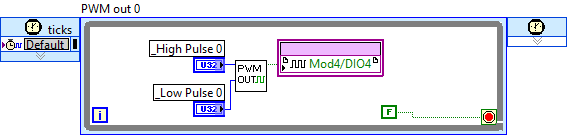

For custom FPGA personnality, it is possible to use PWM scaling: in the system definition, you can define the PWM period (in Ticks), and then at execution, you can play with the ratio (channel value in %):

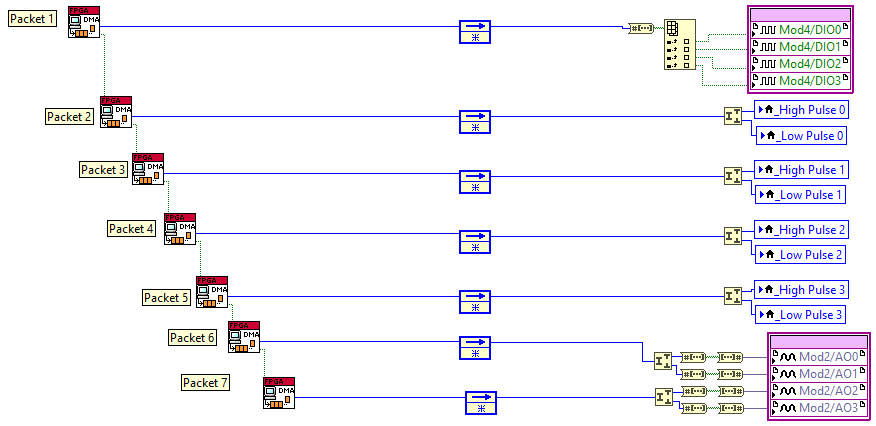

I guess the "native" FPGA scaling inludes the conversion between pulse ration specificed by the channel and the period in ticks to get the high and low time used in the FPGA (_High Pulse x and _Low Pulse x in FPGA example project) :

I am facing for the third time (at least) a customer need to adjust this PWM out frequency at run time. I already adress this need by exposing high and low time in a Custom FPGA Personality. But that's not really convenient (I used to build a display template to get an easy way to configure the whole PWM generation - I'm not sure I even wan't to know if and how is possible with UI Manager).

My proposal : expose PWM period or frequency as an additional (and optional) channel, in order to allow the change of its value at run-time. The FPGA "interface" in VeriStandStand could take in charge the computation of high/low time according to this new channel value. This way, existing FPGA personnality do not have to be changed (backward compatibility).

Cherry on top of the cake, you can even imagine to set up the expected PWM Loop rate and express the frequency in Hz, instead of the PWM period in Ticks (scaling, one more time).

Under the System Explorer, a right click on the PWM out channel could expose a new entry in context menu, allowing the user to Add PWM Frequency Channel (just like Add Information Channels for XNET frames)

Regards,

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.