- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Veristand scan engine interface use FPGA error "LabVIEW" - Noexistent

Solved!06-30-2022 07:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Hello I want to use the FPGA in Veristand. I followed this link to do it :

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA03q000000YGlLCAW&l=en-US

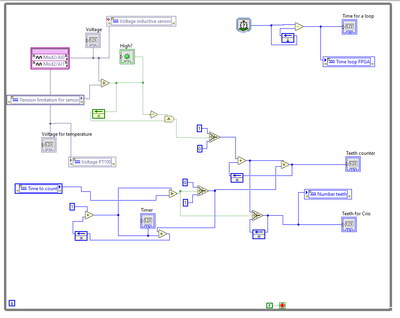

I finished my labview programm, here it is :

I compile it and now I'm back on veristand.

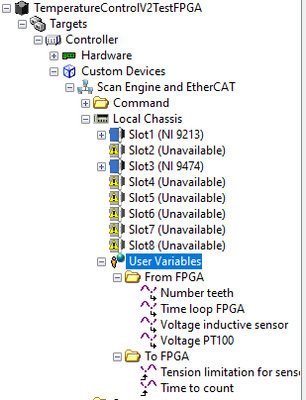

I added the code on user variable :

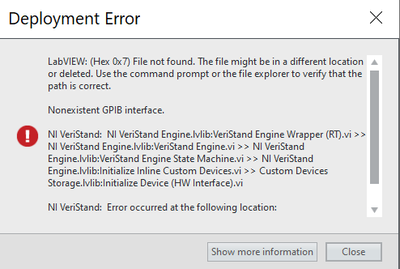

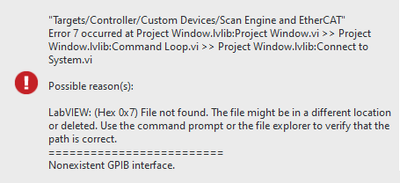

I see the variables from the fpga. But when I try to deploy/run, a error comes. I check on the net, and they said to delete the sowftware on the cRIO and reload it. So I did it and come back to Veristand but no difference.

Thank you very much for your help

Leo

Solved! Go to Solution.

06-30-2022 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Maybe the error that I do is : I delete all the programm on the cRIO and after download all. Maybe I have to delete juste some of them?

06-30-2022 02:21 PM - edited 06-30-2022 02:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That deployment error could mean a number of things, but most commonly this hints that there's an external file reference (a path to something) in your System Definition that is not correct.

Maybe the quickest way to check for this is go back through whatever System Definition configuration you have done and double-check all of the file paths to make sure they are correct.

The prime suspect would be the disk path to your compiled FPGA bitfile...

NI - Chief Product Owner - VeriStand

06-30-2022 06:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Reproduced this problem doing something similar to what you did with User Variables and 3 modules.

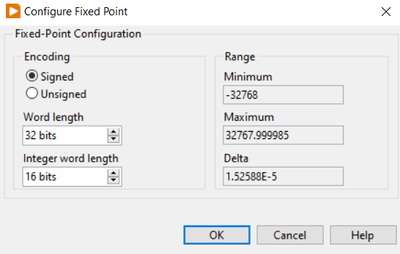

This error started happening when I began using a Fixed Point (FXP) Type I/O Variable.

By default when a User-Defined I/O Variable is created, and you change to the FXP type, the specific type is set to be 64-bit in size:

That leads us to this known issue:

https://github.com/ni/niveristand-scan-engine-ethercat-custom-device/issues/175

which talks about EtherCAT, but now I'm convinced this issue applies to cRIO I/O as well.

Workaround: Set your FXP type to 32-bits or smaller

Use the Configure Fixed Point... button to change to something like at <+/-, 32, 16> set up like this:

Save, recompile your bitfile, update your System Definition, and then your next deploy should work like a charm.

NI - Chief Product Owner - VeriStand

07-01-2022 09:12 AM - edited 07-01-2022 09:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

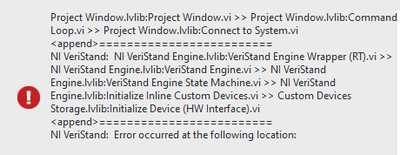

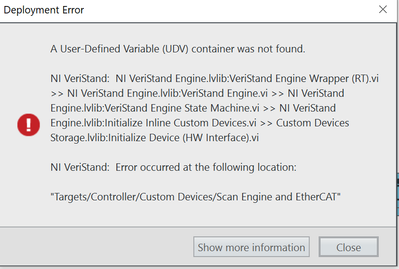

Thank you very much fow your very good answer. So Yes it was the problem. However now, something else appears.

I go check on the net, and it said that is caused by wrongs names. However I compiled, recompiled, tried things but nothing is working. https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000g1sISAQ&l=en-US

If you know, it will be, I think my last problem 🙂

Léo

07-01-2022 11:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That's a new one to me.

That KB is right on the money though

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000g1sISAQ&l=en-US

Did you use a non-English version of LabVIEW to compile the bitfile perhaps?

NI - Chief Product Owner - VeriStand

07-03-2022 09:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have LabVIEW in english so I suppose that the compile is in english? I know that I have labview 32 and 64 bits 2021 installed on my PC maybe it is the problem to have both? I will retry monday on work.

Thank you for your help

Leo

07-04-2022 01:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I will ask an another question on the forum maybe somebody will know 🙂

Thank you for your help

Leo

07-05-2022 01:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I saw when I compile it is written, compilation labview fpga 2020. But I have labview 2021 maybe it is the problem?

Thank you

Leo