- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CompactRIO and system identification

01-16-2012 05:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

I am beginner Labview user, we have a CompactRio at the Lab, and i am attemting to do some system identification. I am having the following questions/issues:

First, i initially built a VI that create a step input "as initial procedure" via an analog output from CRIO into a system, the output of the system is fed back to the analog input of the CRIO, what i have, is i can see the step and the output signals generated on the Oscilloscope, but in my VI it does not give me TP model "the identified model" using the TP system identification "parametric". How do i retrive my model, i searched for some tutorial or some example but all i see is the DAQ assitant tutorial, which bring me to my second question

Because of the issue above, i wanted to use the DAQ assistant, why doesn't DAQ assistant recognize any ports in CRIO, my CRIO is connected to the project...can i use this assistant for the system identification above.

Some example tutorial or the likes would be great.

I am attaching the files...please let me know if u can spot the isse

I appreciate the response folks

01-16-2012 11:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Are you trying to identify the serial # of your cRIO on a network?

The DAQ assistant is for a DAQ, not a cRIO. Think of the cRIO as a more capable/complex DAQ.

Attach your entire project, including your subVI's . You cant get any help when you have over 50% of your files missing. Also, what version of Labview are you using?

01-16-2012 12:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Fernando0901 wrote:

Are you trying to identify the serial # of your cRIO on a network?

Attach your entire project, including your subVI's . You cant get any help when you have over 50% of your files missing. Also, what version of Labview are you using?

Hi Fernando - I think you've misunderstood what was asked here. System Identification refers to determining the mathematical behavior of a system by applying an input and measuring the response, then using the measurements to calculate parameters for a model. The missing VIs are from an NI toolkit that helps with this (unfortunately I also do not have that toolkit installed, so I can't answer the original question).

01-16-2012 12:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you Guys for the response...

Indeed Nathand, i am trying to identify a second order dynamic system, with either transfer function estimation or any other parametric estimation. My issue is that i know i am implementing the correct the components, i generate a square wave "then a PSRB later" corerctly cause i can see it on yhe oscilloscope as well as inside the loop of the VI "target VI, which is the real time CRIO CPU, not the FPGA" , so like i said i have my response and the stimulus inside the loop but no values outside the loop, cause when i try to plot in graph there is nothing...which obviously won't give u any TF.

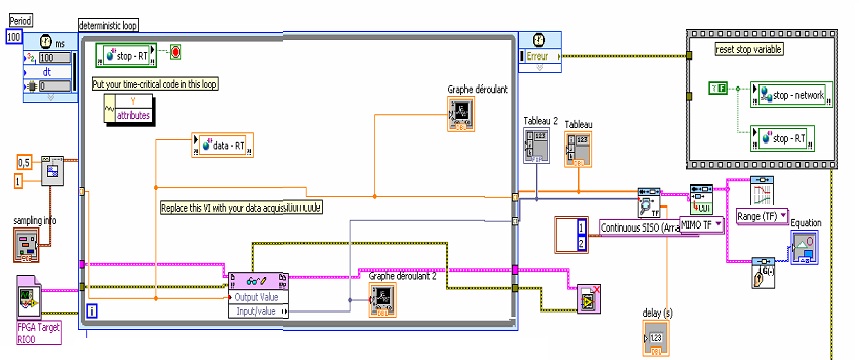

Because i have the files at the Lab, i will attach them tomorrow, but i have now a shot of the target VI. I also i am confused about how to adjust the correct loop time while considering the sampling time and window size "number of points".

Can anybody please, explain how the while loop period affect the sampling time, i mean i have shallow understanding.. I appreciate it...very much

01-16-2012 01:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You'll want to unmark my post as a solution - there's an option to do that. Otherwise other users will see that this thread is answered, which makes it less likely that they'll read it. Sorry I can't be more helpful, I don't have access to the system identification toolkit.

01-17-2012 03:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi E-warrior,

Thank you for posting on National Instruments' forum.

The sampling time is defined in FPGA VI. In your RT VI, you take each sample (in FPGA VI) a the loop period (in RT). That's why you don't take each value sampled on FPGA VI.

I invite you to foolow these links :

Regards,

Romain P.

National Instruments France

01-17-2012 09:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you Romain for your response

So If i understood correctly, i have to make that loop in RT have the same period of sampling time in the FPGA, i'd have to specify either the sampling time in the FPGA in accordance with the loop time... it makes sense definetly, but where do u modify the loop time, is it up to the right as shown in the picture "the 100 ms one", can you please be specific.

Thank you very much

01-17-2012 09:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

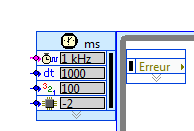

It's up to the left

Double click on the watch icon, or set up a value on dt parameter. (1000 on dt = 1000ms, 100 on dt = 100ms, etc... on the base clock 1kHz)

Regards,

Romain P.

National Instruments France

01-17-2012 10:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you Romain,

Sorry I think i am missing a point here, what is the relationship between the base clock and the dt, which one is responsible for the period between each iteration of the while loop, and the ohter does what exactly

Thank you Romain

01-18-2012 02:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The base clock is the reference clock of your timed loop (a software clock in your case given by the controller). The dt parameter makes you able to choose the time between each iteration : it's the period of the timed loop given in ms.

Regards,

Romain P.

National Instruments France