Configure Sample Rate of Single Cycle Timed Loop in LabVIEW

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW FPGA Module

- LabVIEW

Software

Code and Documents

Attachment

Overview

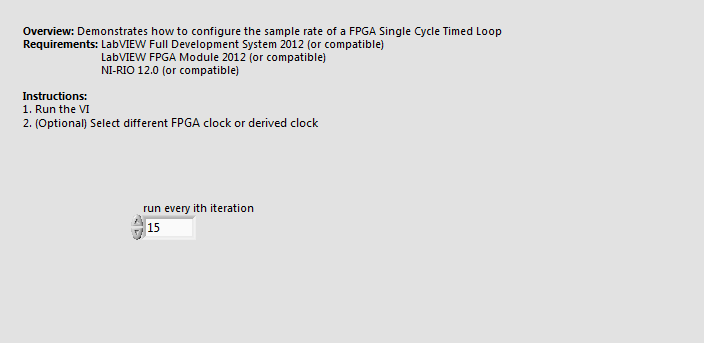

This example demonstrates how to configure the sample rate of a FPGA Single Cycle Timed Loop

Description

Creating a FPGA derived clock allows to generate custom update rates for applications. If the desired clock rate is below the range of the FPGA derived clock (<2.5 MHz), it is possible to generate a derived clock with a higher frequency. Using a Single Cycle Timed Loop (SCTL) with empty iterations is one possiblity to achieve the desired rate.

One example for achieving the CD sample rate of 44.1 kHz, a derived clock rate of 47.407 MHz (32/27 * 40 MHz) can be used and with executing each 1075th iteration of a SCTL, which gives you 44.0999 kHz. One alternative solution is configuring the "Wait" function and waiting the number of ticks.

The VI calculates all possible FPGA derived clock rates returns the best fitting rate of the derived clock with the number of ticks to wait and the occuring error of the clockrate.

Note that at the low end of the derived clock (2.5 - 5 MHz) not all combinations of the derived clock are possible. You need to test it in the actual FPGA Derived Clock dialog to verify.

This example shows how to calculate the derived clock and the number of iterations of the SCTL to archieve the desired sample rate:

Requirements

Software

- LabVIEW Full Development System 2012 (or compatible)

- LabVIEW FPGA Module 2012 (or compatible)

- NI-CompactRIO 12.0 (or compatible)

Hardware

- No hardware is necessary to use this example VI

Steps to Implement or Execute Code

- Run the VI.

Additional Information or References

**The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text 'NIVerified'. Read here for more information about the new Example Guidelines and Community Platform.**

Applications Engineer

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.