- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Model Execution Order

Solved!12-14-2011 01:12 PM - edited 12-14-2011 01:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The VS 2011 Help states:

************************************

Model Execution Loop(s)

Each Model Execution Loop executes a corresponding compiled model. The number of Model Execution Loops is determined by the number of models specified in the system definition file. Per iteration, each Model Execution Loop executes the following tasks:

- Reads the data sent by the Primary Control Loop and maps this data to model inputs.

- Executes one step of the model.

- Reads model output values and sends this data to the Primary Control Loop.

**************************************

Let's assume that :

- I have 3 models such as each model's output is fed into the next model's input: Model 1 >> Model 2 >> Model 3

- with corresponding channels mapping such as:

Model1_output <----> Model2_input

Model2_output <----> Model3_input

- Execution order is set to "parallel"

- Model Decimation is set to 1 for all three.

Will the three models execute within the same PCL tick "in parallel" in the PCL loop context, while executing in series within the tick time slice due to the way the channel mapping is defined?

Thx.

L.

Solved! Go to Solution.

12-14-2011 01:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

No. Channel mapping does not determine execution order. In parallel mode, all three models receive identical inputs from the PCL. These inputs are based on the previous iteration of the system. The model outputs from iteration (N-1) update the PCL at the beginning of iteration (N), and these updates are available as model inputs during iteration (N).

In your case:

Tick 1

Write A to model 1, model 1 executes and writes A' to PCL

Tick 2

Model 2 gets A' from PCL, executes and writes A'' to PCL

Tick 3

Model 3 gets A'' from PCL, executes and writes A''' to PCL

If this is undesirable, you should put the models in series from the Execution Order category under Simulation Models in System Explorer. This makes the model outputs available to the other models in the same iteration of the PCL. Note, it does not make the model outputs available to the rest of the system until the next iteration of the PCL.

Steve K

12-14-2011 02:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ok Thx Steve,

...and the execution order will give me as many "groups" as I have models I suppose, correct?

Now to complicate this, here is the next curved ball:

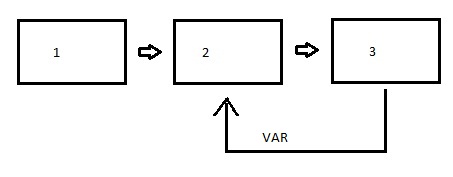

I have my 3 models set up like you indicated. Now let's assume model 3 has an output (VAR) that must be fed back into Model 2 like on the image above. Will the behavior of the execution be as as follows ?

- tick 0 : model 1, 2 ,& 3 initialize with whatever init values are set in the system, including VAR

- tick 1 : model 1,2, 3 execute, with model 2 using Var(t=0)

- tick 2 : model 1,2, 3 execute, with model 2 using Var(t=1)

etc...

L.

12-14-2011 02:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Correct. With three models in series, there will be a one tick delay between when model 3 outputs VAR and when VAR is available at model 2. As you know, all bets are off if your loops are late.

Steve K

12-14-2011 03:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

in addition to the correct things stated so far about model sequencing... you can also change a controller setting to eliminate the 1 cycle delay of PCL communication to/from the model. That setting is "low-latency" execution mode

with that set... then inputs to the models and outputs from the models are written/read in the same step of the PCL. This means if your model outputs 5 and that is mapped to AO, within the same tic... AO will be 5. This is contrary to the default "parallel mode" where one tic later AO would actually be 5. Also, since hardware inputs will be acquired in the same tic before models execute... any hardware inputs mapped to models will send this actual hardware data to the model for the first tic instead of the default input value as parallel mode does.

Obviously as you change things to have less parallelism... you reduce your max loop rate though. Think of it as pipelined logic vs combinatorial logic 😉