- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Master Hardware Sync

Solved!12-15-2011 12:58 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In the System Definition File, under Chassis, there is a setting for Master Hardware Sync Device. The VS docs describes it as:

***************************

Setting a Chassis Master Hardware Synchronization Device

A chassis master hardware synchronization device controls the synchronization of all hardware in a chassis and must be an NI-DAQ device with at least one analog input or output channel, any NI FPGA, or a timing and sync device that has the capability to drive the 0 line. The RTSI 0 line is a digital line that sends a clock signal that synchronizes all hardware I/O devices in the system.

Complete the following steps to set an NI-DAQ device as the chassis master hardware synchronization device.

**************************

In general terms, when is is required to use one of the DAQ device to do a harware Sync? As soon as > 1 card is used ? Does the RTSI lines are used transparently to time the PCL and DIOs?

More specifically:

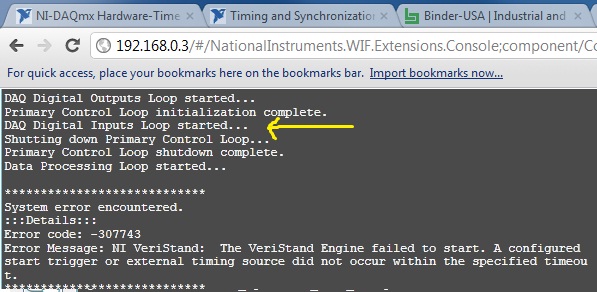

I have been having the following error occuring at deploy time: Error -307743:

One can see that something goes wrong iwth DAQ DI Loop is started.

This error did not use to occur, and I deployed this file 10s and 10s of times without issue.

My system has 2 cards :

- PCIe 6343

- PCI 6723

First thing I did it to remove the DI from the 6723, the system deployed fine once, then the error came back

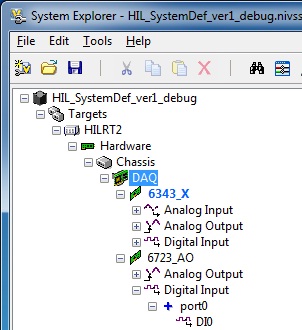

Finally, I looked at the sync settings. They are set like this:

Setting them back to None, deployment worked. Then I set them back to DAQ, like on the above, and all worked fine again.

Digging in this a little more, I noticed that if Export Sample Clock is set to ao/sample clock the error is back, despite the presence of an AO channels in the list...

Are you aware of any tricks or system definition file error or corrpution with regards to these settings beside the info what is found the VS docs ?

Thx.

Laurent

Solved! Go to Solution.

12-15-2011

01:20 PM

- last edited on

04-23-2024

05:49 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You will have unexpected behavior if you are using PCI hardware and not connecting the hardware with a RTSI cable.

The timing master device is designated with bold blue as shown on your screen shot. That device, as stated in the help, has to be one that has at least 1 AI or AO. That device then needs to send its hardware sample clock to other analog (analog only!) devices in the system. That means if you have other devices in your system that use AI or AO (and do not have the "disable hardware timed single point" checkbox checked)... they will expect to see the sample clock on PXI Trigger 0 or RTSI 0.

If you're using PXI... the sample clock is exported from the master onto PXI Trigger 0 and everything in the same bus segment of the backplane will see this automatically. If you're using PCI... then you must either disable hardware timing (not recommended) or acquire an NI-RTSI cable and follow this procedure that I just wrote for a colleague. (Ideally we need to put this in the help in the future)

- Select the chassis page and designate (your multifunction DAQ device) as the chassis master.

- In MAX, find your remote system and expand devices and interfaces

- Right click the chassis and select Identify -> External PC

- Right click devices and interfaces and select create new

- Select NI-RTSI Cable and select finish

- Right click the new NI-RTSI cable and add your analog devices to the RTSI cable. Just these devices are required because they are the only devices with AI or AO that is hardware timed (however some boards do not support hardware timing like the 6704... which I don't recommend using)

- Physically install an NI-RTSI cable between the devices

12-15-2011 02:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ha ! now I know where the heck that bold blue was for !

So...ok I need to define the RTSI cable in MAX.

So in VS, just to be 100 % clear, the Master Hw Sync Device settings: does they have to be done for each card in my system ? or just for the Master?

Something that looks buggy to me is this: My Export Sample Clock box is set to ai/SampleClock and DAQ Devcie = 6343. Now if I select 6723 instead, the Export Sample Clock changes to ao/SampleClock. Then if I switch back to 6343 it stays at ao/SampleClock and leads to the errors I was talking about. Taa taa!

Laurent

12-15-2011 03:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

yeah that ao/sample clock thing looks like unexpected behavior to me...

It is because the 6723 doesn't have AI channels so it only has an ao sample clock... but your 6343 isn't using the AO sample clock... it only uses the ai sample clock if ai is present (and clocks the ao with the ai sample clock)

No. you just pick a master on the chassis page and set it up. all the default settings should be fine. THe slaves are every other analog card and they wait for a sample clock on rtsi0