- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

USRP 2954 TX-RX loopback delay

06-27-2018 01:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear all,

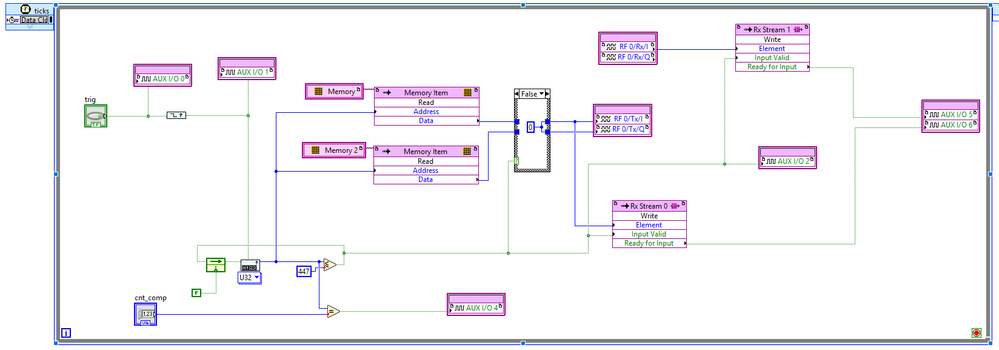

I am using one of the simplest Labview FPGA vi. I intend to transmit 10 periods of sine wave with the TX port of a daughterboard, and receive the same signal with the RX port of the same daughterboard (model UBX-160). The signal is transmitted either through leakage, or with a short cable.

I am using a 448 sample length ROM from which I read the the samples, while incrementing the adress with a counter. The counter is triggered on the falling edge of a host delivered trigger. Two FIFOs exist, one on the samples of the transmit path, and the second one for the samples of the received signal. It is clear that the input valid signal signal is the same for both FIFOs, and lasts for 448 clock periods.

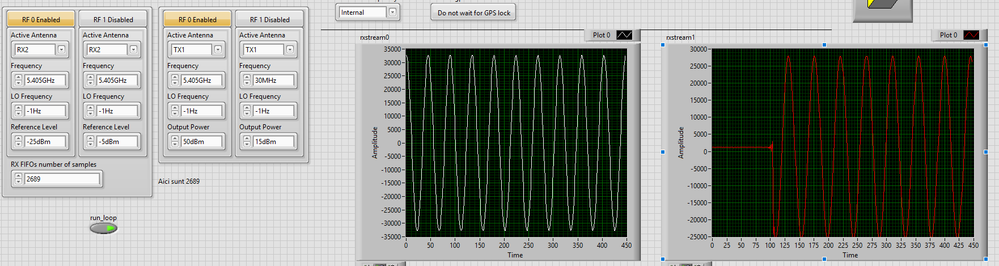

The issue is that there is an approximately 100 clock period delay between the signals in the FIFO. I expected this delay to be much shorter. The even stranger part is that this delay is 100 clocks period even if I use 120Msps or 200Msps sample rate.

Please have a look at the described vi and at the front panel capture:

Best regards,

Mihai

07-02-2018 08:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Mihai,

Do you see the same delay when using the Simple NI-USRP Streaming example found in C:\Program Files (x86)\National Instruments\LabVIEW <your version>\ProjectTemplates\Source\NI-USRP\Simple NI-USRP Streaming?

Partner Development Engineer

Alliance Partner Network

National Instruments