- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Override PXI-1033 backplane clock with PXI-6653 OCXO clock

Solved!01-07-2015 04:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I need a a more accurate 19.2MHz clock from a PXI-6653. Supposedly, it is possible to override the PXI-1033 backplane clock with the a clock from the PXI-6653 OCXO. It is not clear to me how do do this. NI literature suggests i may need some SW. Thanks!

Solved! Go to Solution.

01-08-2015 12:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can PLL your backplane to your OCXO clock using NI Sync, specifically the niSync Connect Clock Terminals.vi. You'll want to connect "Oscillator" (source) to "PXI_CLK10_IN" (destination). There's a LabVIEW example (help->find examples->search "pll") which first tries to PLL an external clock to the backplane and then PLL's the onboard oscillator if no external clock is found called "Check Clk10 & Route Clock.vi." If you look at the case where no external clock is found you'll see how to PLL its onboard oscillator to the backplane, which was also described above.

01-08-2015 04:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi John:

Thank you for the help. What you are suggesting is very logical, but the best I can do (w this vi) is to get the 10M (OCXO) to clk out...but I cant seem to use the OCXO to clock a 19.2MHz from the DDS at clk out. Using other vis, I can produce a 19.2MHz signal but based on the frequency error, it is running off of the backplane clock. (Based on leakage seen via a spec an, i can see that the backplane clock is used...the frequency error is too high vs. an OCXO.) This should not be difficult, I dont know why Im struggling with it.:![]()

ted

01-08-2015 05:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This board is designated for the NI Signal Generators family. These are device typically having a name like NI 54xx. I would try posting your question to the PXI board, as I think the Timing and Sync devices are more relavant there.

http://forums.ni.com/t5/PXI/bd-p/270

I'm not entirely sure if this will work because I don't have the HW, but as jmoody suggests, use the Check Clk10 & Route Clock.vi . I think ClkIn uses whatever EXTERNAL clock you are providing to the 6653. Since you want to use the OCXO that is INTERNAL to the 6653, I think you need to change that constant on the block diagram to Oscillator. If that doesn't work, query the above message board.

National Instruments

01-09-2015 01:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

OK, it seems to work now, thank you for the helpful comments. Someone suggetsed on-line (with a helpful picture) to set the 1033 backplane jumper to the "up" position...this opened up the PXI_CLK10 path - replacing the backplane clock with the the OCXO clock...I now get what i was looking for, a very (frequency) accurate 19.2MHz clock from the DDS.

01-09-2015 01:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The phrase "backplane clock" usually refers to the PXI_Clk10 signal in a PXI chassis. Overriding that clock with a 19.2 MHz signal is a bad idea. (It breaks the PXI specification, and may result in strange behavior.) Instead, you should use the PXI_Star lines to distribute that signal to other slots.

James Blair

NI R&D

01-09-2015 01:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Oh, thank you, good idea.

01-09-2015 02:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

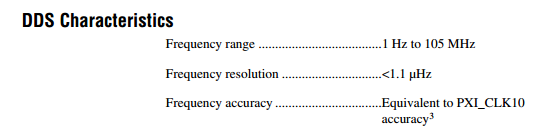

I agree with James on his comment. From reading the OP's post, I was under the impression that he was just trying to override the PXI backplane clock with a 10MHz clock to generate a more accuracte DDS signal from the 6653, as per the specifications manual:

http://www.ni.com/pdf/manuals/370711b.pdf#page=46

Jason L.

National Instruments