- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Write on DMA FIFO sbRIO 9606

Solved!11-01-2017 05:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

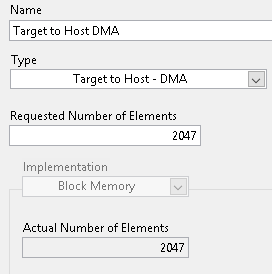

I have 2 FIFOs, both set up like this

One target to host and the another one host to target. My work consist in encrypt files using the target, both that isnt the problem. When I write(in host) and read the proccesed information of 10,000 bytes works fine, but when i try to encrypt files of ~25 Mb i got an error. I have observed that modifing my time loop period (i have 10 uSec) (in target vi), i can process larger files. So i have some doubts.

1) Why if my file is bigger than 2047 elemnts, works fine? and Why if my file have ~25mb doesnt work?

2) How the loop period intervenes on my cycle?

Solved! Go to Solution.

11-02-2017 03:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You might want to consider posting in a different forum, not a signal conditioning one. Instead, you can post to FPGA forums or even in LabVIEW forums.

1. Remeber DMA enters registers in memory, A DMA FIFO allocates memory on both the host computer and the FPGA target, yet acts as a single FIFO. DMA FIFOs provide performance advantages over using front panel controls and indicators to communicate between the host and the FPGA.

Assuming of course that the FIFO on the FPGA is big enough to avoid overflows, I'd expect the dominant factor to be the size of read performed on the host. In general, larger reads on the host lead to improved throughput, up to the speed of the bus. This is because FIFO.Read is a relatively expensive software operation, so it's advantageous to make fewer calls to get the same amount of data.

Note that the larger your call to FIFO.Read the larger the host buffer needs to be. Depending on your application, it might need to be several times larger than the read size. You can set the buffer size with the FIFO.Configure node.

http://zone.ni.com/reference/en-XX/help/371599H-01/lvfpgaconcepts/fpga_dma_how_it_works/ explains the various buffers involved. It's important to note that the DMA Engine moves data asynchronously from the read/write nodes on the host and FPGA.

2. Your loop period will be the one determining the time to execute