- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

sbrio 9631 digital inputs/outputs using FPGA I/O Node and FPGA I/O Method Nodes

Solved!06-20-2011 02:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

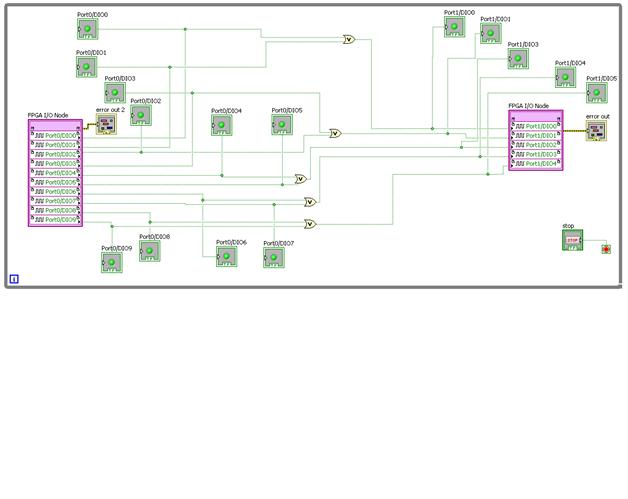

Hello, I am trying to configure my SBRio-9631 for the first time. I am trying to use the on-boards digital inputs and outputs. Will the following coding work? This is a simple 'read the inputs, 'or' some inputs and pass it out to the outputs'. Would I need to add 'FPGA I/O Method Nodes' between my 'FPGA I/O Nodes' to get the 'Tri-state modes for the input and output lines? Also, I am having trouble simulating/testing this to work, by adding 5Vdc to the inputs and not getting any output voltage source. Thank you for your time.

Solved! Go to Solution.

06-20-2011 11:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Take a look at this tutorial.

06-21-2011 09:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you very much for this helpful information. I have a specific question. I am going to use my SBRio-9631 to replace Texas Instruments SN74LS244N (non-inverting buffer) that takes signals from one PCB to another PCB. Can I configure my on-board inputs and outputs as Tri-state? Is the 9631 digital I/O Tri-state compatible? Please reference the image below showing the code I have written so far. Should I insert FPGA I/O Method Nodes between my two FPGA I/O Nodes and set the 'Set Output Enable as True' or should I put the Method Node after my output I/O Node to get Tri-state outputs? Thank you for your time. If you have any questions about the image below, please let me know.

06-21-2011 10:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have modified my vi block diagram to include FPGA I/O Method Nodes for the outputs of my sbRIO-9631 on-board digital outputs. Setting the 'Enable' to 'True', would this make my outputs Tri-state now? Please refer to the image shown below. Thank you for your time.

06-21-2011 02:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please read through this help document on Using FPGA I/O. It summarizes the method for using Output Enable to toggle a Tristate DIO line through its modes of input and output.

What do you intend to enable by making your outputs "tri-state"? Tri-state is an an adjective to describe a logic pin that can drive 0 and 1 logic levels as well as a third, high-impedance state, typically used for input or to allow other circuits to drive a line. All the DIO lines on the sbRIO-9631 are capable of tri-state logic. Setting Output Enable = False makes those DIO lines high-impedance (non-driven).

Cheers,

National Instruments

To the pessimist, the glass is half empty; to the optimist, the glass is half full; to the engineer, the glass

06-22-2011 11:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your information. It was very useful and I made a simple vi showing what I believe the material is stating (please see the image below). When input Port8/DIO0 goes 'high', the output signal enables the Method Node to 'true' and enables the output of Port9/DIO0 to go 'high'. When the input Port8/DIO0 goes 'low', the output signal enables the Method Node to 'false' and the output of Port9/DIO0 to go low and 'high impedance'. The outputs of my sbRIO-9631 need to go to 'tri-state' in order to interface with other 'bus' devices like 'buffers' and 'line drivers'. Is this image correct? Thank you for your time.

06-23-2011 10:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi gjmm,

The code you've written should perform as you described. How fast do you need this logic to react to changes in the input? Without any timing mechanism in your code, this code will run as fast as it can compile. I would expect this code to run somewhere between 1-5MHz, if I had to guess.

If you need it to respond faster, you could place the code within a Timed Loop. In LabVIEW FPGA, a timed loop is known as a Single Cycle Timed Loop, and it executes once for each clock tick of the FPGA. By default, that would be 40MHz on an NI Single-Board RIO.

Regards,

National Instruments

To the pessimist, the glass is half empty; to the optimist, the glass is half full; to the engineer, the glass

06-23-2011 10:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Spex,

I really, really appreciate your help. Your follow-up information on this topic was exceptional.

Thanks again for your help and time.

gjmm