- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Synchronize two FlexRIO controllers FPGA

07-03-2019 03:58 AM - edited 07-03-2019 04:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I'm writing here as I need to synchronize data generation and acquisition in two FlexRIO controllers with FPGA.

I've got two FlexRIO controllers with NI 7935R FPGA cards and NI 6589 Digital I/O adapter modules. I need to synchronize both FPGA so I could run single cycle timed loops at the same clock frequency. My idea is that one FlexRIO should feed its own FPGA with the clock, and it should also export the clock to the other FlexRIO.

I found that I can use strobe and clk_out digital lines to export and import LVDS clock to the DIO adapter module, however, I look for a simpler solution. I wonder if I can use the "clock ref" input from the FlexRIO controller box, instead of the digital lines to and from adapter module? I assume there may be such an option but I didn't find how to do it.

Thanks for help!

Kind regards,

Anna

08-03-2019 12:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Anna,

I have a 7935R, but with a different adapter module, and I am just staring to learn more about clocks on FPGAs and synchronizing them. An approach to consider is getting an external clock manager/distributer and connecting it to the two flexRIO and adapters, so 4 clocks being sent out.

-Mark.

08-03-2019 12:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Anna,

I have a 7935R, but with a different adapter module, and I am just staring to learn more about clocks on FPGAs and synchronizing them. An approach to consider is getting an external clock manager/distributer and connecting it to the two flexRIO and adapters, so 4 clocks being sent out.

I'd have to look more into what you suggested and read more about the approach I mentioned. But maybe this is something to look into.

Best,

Waffles.

08-06-2019 10:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Anna,

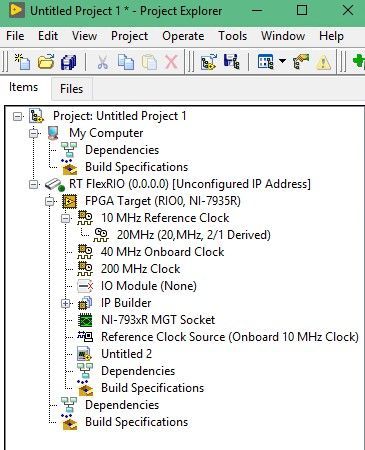

basically the most convenient method is to use a reference clock for synchronisation. For the 7935 controllers, I don´t see a capability of exporting a ref-clk, so I think you need to use a external 10 MHz ref clock and connect it to both of your controllers in order to sync them to the same 10 MHz clk signal. This allows you to create a FPGA base clock from the REF IN Port and derived clocks as you need.

best regards

M. Brauner NIG

08-07-2019 05:12 AM - edited 08-07-2019 05:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your reply Mark and Marco.

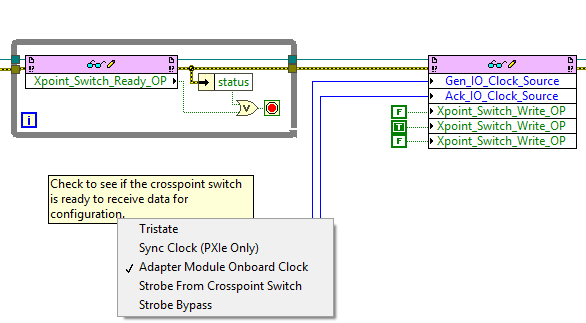

I considered the use of ref clock at the beginning, but I want to configure the controller to use NI 6589 adapter module Serdes Channel DIO interface. In this case, I'm forced to select I/O Module Acq/Gen Regional Clock as a clock source of single cycled timed loop in FPGA. Otherwise, the compilation doesn't proceed. Then, in RT, I can configure this clock to one of the options shown in the enum below.

From the above I conclude that I can either use internal Adapter Module clock to feed my single cycle timed loops, or I can use Strobe LVDS line from the Adapter Module I/O connector and send external LVDS clock through it. The second solution, however, would force me to make changes in my PCB, as I mentioned earlier.

I wonder if I can feed the clock from 10 MHz ref clk. I created it in my project, but I can't configure it so the I/O Module Acq/Gen Regional Clock would use it. Maybe I miss something?

Kind regards,

Anna

08-07-2019 08:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Anna,

after digging a bit deeper, I figured that the best solution to sync two 6589 FAMs would be to use their "DDC Clock Out" and "STROBE" signals.

The configuration is done in the examples "ContGenExportClk" and "SerialAcqConfig". You find those in your respective LabVIEW examples folder

(i.e. "C:\Program Files (x86)\National Instruments\LabVIEW 2018\examples\FlexRIO\IO Modules\NI 6589")

I think with this FAM, you have to take its Double Data Rate behaviour into account. So clocks should be only half. (1Gbps --> 500MHz clk)

Marco Brauner

Senior Applications and Systems Specialist

08-21-2019 08:49 AM - edited 08-21-2019 08:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Marco,

Actually this was my primary question whether I can solve the problem in a simpler way than that. I hoped to omit the fact that I would need to modify my PCB in order to use clk_out and strobe lines. I hoped to use e.g. "ref in" in the FlexRIO chassis instead.

But thank you for trying to find the answer,

Best regards,

Anna