- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PXIe-782XR digital output failure detectability

Solved!10-15-2019 10:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I am considering using PXIe-782XR cards for a safety critical system. The FPGA has a large number of digital IO: most would be used as inputs and a few as outputs. To drastically simplify: if state of any input transitions to low level, one of dedicated outputs would also be forced low.

It would be beneficial for me to detect in the FPGA if an output stage on the card fails (the critical failure mode would be if it latches high). Mitigating the failure is not required (that is done elsewhere in the system), but detecting the error in the FPGA and reporting it to the host would be very nice. Of course, cable integrity etc is also out of scope here, I am purely interested in the output buffer failure detectability.

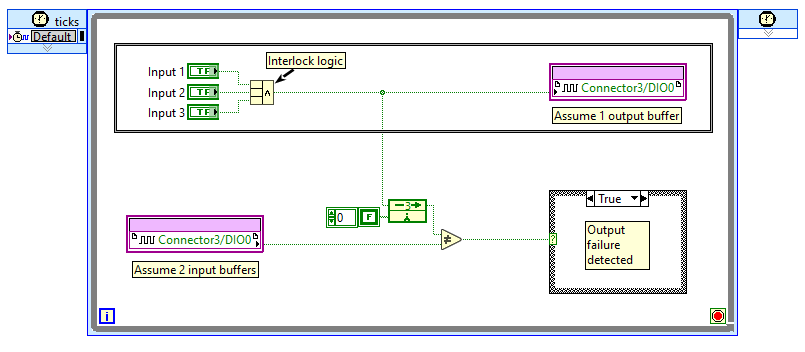

My understanding is that the 128 DIOs on the card are bidirectional buffers (see https://www.xilinx.com/support/documentation/user_guides/ug471_7Series_SelectIO.pdf page 39). I would like to understand what happens if I am writing to and reading from the same digital output in a SCTL (see example image). Would the data just be read from an intermediate internal register (what does LabVIEW do here?), or would I actually read the logic level from the wire connected to the card's front panel, despite also writing something to it in the same cycle?

Cheers

Solved! Go to Solution.

05-15-2020 04:26 PM - edited 05-15-2020 04:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello ToKoSi,

You should use Set Output Data and Set Output Enable methods.

Take in mind that in SCTL (Single-Cycle Timed Loop) the entire contents of the loop will executes within one tick of the FPGA clock you have selected. So try to perform read and write functions not in the same tick.

This two articles will give answers to your questions (links are below) more detailed.

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z0000019NgvSAE&l=en-US

The best way to thank, is to give KUDOS

05-16-2020 08:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello ToKoSi,

In addition to my last comment:

The logic in the screenshot example will work, just keep in mind that you should ignore first three ticks in this case.

The best way to thank, is to give KUDOS