- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 5732 Acquisition

Solved!05-07-2015 05:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

I have a NI 5732 used with NI PXIe 7962R, and they are embedded in an NI PXIe 1073 chassis. I wanted to test the data acquisition so I connected a function generator to the AI0. However, something weird happend. The acquired data seemed to be the derivate of the signal sent from the function generator: the sine was still sine, but the square wave became pulses, and ramp became square wave! Has anyone saw this happening before? Thank you!

Best,

Tong

Solved! Go to Solution.

05-07-2015 05:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What was the frequency of the signals you were generating, and what options do you have selected for AC/DC coupling and filtering? If you have the input set to AC coupled or one of the filters enabled that sounds like expected behavior if the signal of interest lies within the band of attentuation.

05-08-2015 01:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi David,

Your suggestion helps me a lot. Thank you! It is the problem of AC coupling. When I set it to DC the acquired signal is correct.

However, another problem arises. When there is no input, the output of FPGA is not stable. It outputs a lot of points having values more than 60000. I think it should stay at about 32768 (=2^15). Why is it happening?

Best,

Tong

05-08-2015 01:53 PM - edited 05-08-2015 01:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What clock domain do the analog input signals reside in? The IO node that you get the AI data from needs to be in the Sample Clock domain (or IO Module Clock domain if you are using an older version of the CLIP). If they're not in the correct clock domain you are performing an unsafe clock crossing which could result in glitching. The glitching is likely what you are seeing.

05-08-2015 03:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm just using the 40MHz on board clock. I think it's the default one. I'm not familiar with the clock domain you mentioned. Could you tell me more about it? Thank you!

Best,

Tong

05-08-2015 05:35 PM - edited 05-08-2015 05:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Open the example finder and navigate to the getting started example at Hardware Input and Output>>FlexRIO>>IO Modules>>573x>5732.

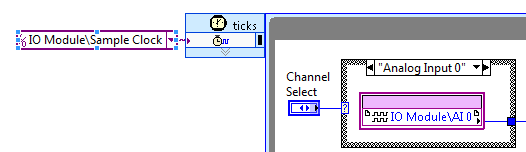

You'll notice that the analog input node is in a single cycle timed loop that uses the sample clock as its clock source. This means that the "clock domain" that the IO node resides in is the "Sample Clock".

When working with a FlexRIO Adapter Module that has an analog input or output IO node, there is usually a specific clock domain that IO node must reside in. You'll want to read the help entry for the CLIP that your specific FAM uses for more information.

05-10-2015 04:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi David,

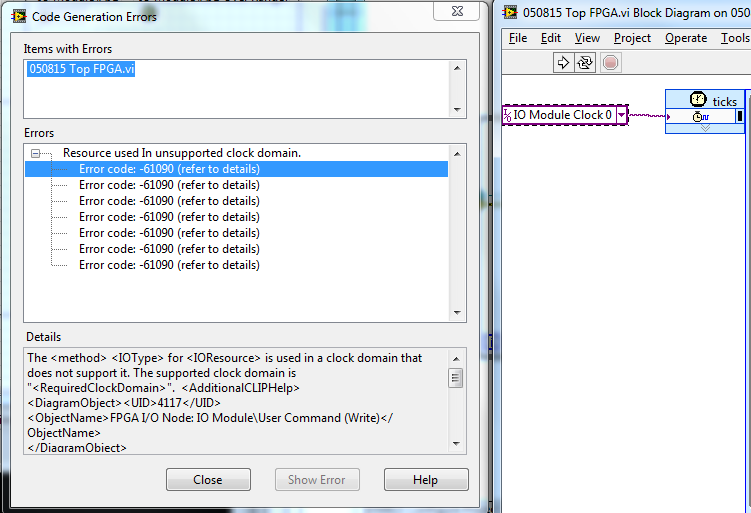

I tried to connect a "IO Module Clock 0" to the timed loop. I'm using Labview 2011 so there is no "IO Module\Sample Clock". However the following error dialog poped up. I already added the "IO Module Clock 0" in the project. What's wrong with it? Thank you!

05-10-2015 09:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The user commands need to be in the 40MHz clock domain.

05-10-2015 09:54 PM - edited 05-10-2015 09:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

*double post

05-11-2015 09:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator