- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to create Derived Clock less than 5MHz in cRIO-9039

Solved!02-28-2019 11:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi experts,

My goal is to run FPGA code using Single Cycle Timed Loop using 3MHz or less frequency. The problem I am facing now is cRIO-9039's FPGA Target appears not supporting deriving the clock to less than 5MHz (1/8 derive rate of 40MHz).

I use IP Integration Node that only supports running inside of Single Cycle Timed Loop so using while loop seems not an option (I tried.. then complained).

The compile result says Maximum possible rate is 3.3MHz. So I should be able to compile my code just fine if I use 5MHz or slower rate.

Thank you in advance

Solved! Go to Solution.

03-01-2019 03:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The problem I am facing now is cRIO-9039's FPGA Target appears not supporting deriving the clock to less than 5MHz (1/8 derive rate of 40MHz).

Are you getting an error? Or is it just not letting you type in a value less than 5MHz?

Program Manager, Hardware Services

National Instruments

03-04-2019 11:31 AM - edited 03-04-2019 11:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

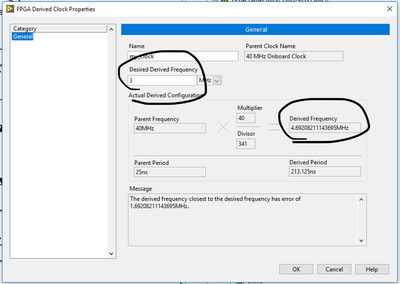

It lets me type the frequency but the adjusted (closest to requested) frequency is much higher.

For example, if I type 3MHz, it's only possible to make 4.69MHz. If I type 10Hz, still 4.69MHz.

03-05-2019 12:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I tried it on my side and 4.69MHz seems to be the lower limit.

I know you mentioned that you were seeing 3.3MHz in the compile results. Could you post a screenshot of this?

03-08-2019 06:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@shrupa123 wrote:

I tried it on my side and 4.69MHz seems to be the lower limit.

So it is the limit. That is all I wanted to know. Is this documented somewhere?

Thank you

03-11-2019 09:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This specification has to do with the VCO operating range of the Xilinx Kintex-7 7K325T FPGA in the 9039. The datasheet for Kintex-7 FPGAs is found here.

Program Manager, Hardware Services

National Instruments