- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Buffer overflow in FIFO read from FPGA

Solved!09-14-2020 04:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I have a problem with FIFO buffer on RT target. When program is running usually everything is fine, I am reading values with requested speed. But from time to time I can notice that inside buffer stays more and more values like program can't read fast enough, buffer reaches its maximum depth and resets after a short while and then program continues running properly.

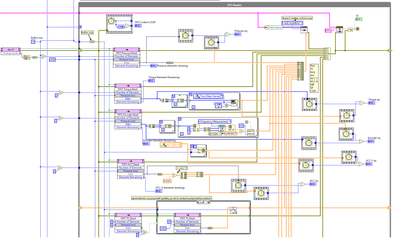

FPGA code:

RT data aquisition code:

I am using Target to Host DMA FIFO settings.

Device: cRIO-9049

Labview 2019

I am new with Labview and I would be grateful for any tips and ideas what can creates this kind of delays in code. And sorry for my language mistakes.

Solved! Go to Solution.

09-14-2020 03:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your screenshots don't really show much of the important stuff (sample rates, buffer sizes). Also, I expect some of the people on here are far more experienced with DMA FIFO than I am and will have specific points.

I can just give you some general things to consider:

- What is the sample rate of data going into the FIFO on the FPGA side and the number of elements in each

- Then look at the buffer length on the FPGA side - from what I remember from helping somebody look at a DMA FIFO problem there isn't just a one value for buffer length that is common to both FPGA and RT (but I could be getting mixed up)

- How quickly (in time) will the buffer filll up with no reading of data out of buffer?

- On the RT side, you will probably be reading block of data, rather than individual elements, so you will keep checking the number of buffer elements until you have enough and then do a read. So the thing to think about is how frequently you are checking the buffer and how many elements you read in one block.

- Are you using a while loop to read the FIFO DMA - and is the RT determinism good enough to provide consistent reading (e.g. if CPU is highly loaded then might start getting reads that are not executed - worth checking execution status).

- What is the buffer length on the RT side, and how quickly would it fill up if you didnt do any reading on RT side?

- Do all these times seem sensible - and have some margin if reads are not completed in time? If not the consider widening the buffer lengths, or how frequetly you do reads.

One of the problems we had was that the FIFO DMA buffer length on FPGA was too small.

For troubleshooting - it might be useful to feed an artificially created sine wave or sawtooth created on the FPGA side and see what you get out on the RT side - as that can allow you see if you are getting occassional blocks of missing data, if consistent, if applies to all signals through the buffer or all buffers.

Hope this helps,

www-isc-ltd.com