From Saturday, Nov 23rd 7:00 PM CST - Sunday, Nov 24th 7:45 AM CST, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Saturday, Nov 23rd 7:00 PM CST - Sunday, Nov 24th 7:45 AM CST, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

09-30-2015 10:50 PM

Hey,

I'm new to Labview FPGA, and I'm using sbRIO9606 to do some experiments. I have a problem with the high throughput sin-cos function. When I use this to do a park and inverse park transformation. It takes all the LUTS resources in FPGA as in the FPGA vi: PWM test.vi

So I tried to put the park and inverse park transformation in the RT and transfer the data back to FPGA. At first I use the direct FPGA read/write function in the RT however, it gives me some results but not right.

Then I try to use FIFO to pass values between RT and FPGA, but I cant configure them the right way.

In the project the PWM test.vi is the one I put everything in FPGA

im_communitert.vi is the vi I tried to pass the angle generated in FPGA to RT and the rt_IMcontrol.vi is the RT host vi

Can somebody please help me out?

regards

10-24-2015 09:06 AM

Hi,

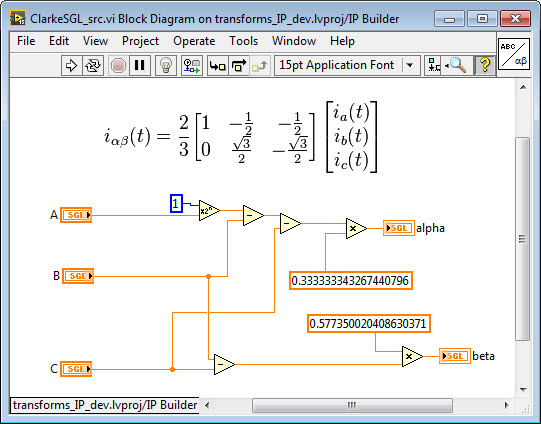

in abctoqd.vi you did not use high throug. function. sin and cos are implemented in double, which must be strongly avoided in FPGA. Even if the result is converted in FXP, evaluation is performed in double.

I closed a field oriented control loop on NI myRIO. Programming should be efficient, in the FPGA resources are very limited.

10-26-2015 12:23 PM

thank you for the reply, is that ok that you send me the park and inverse park vi you use ?

regards

10-26-2015 03:22 PM

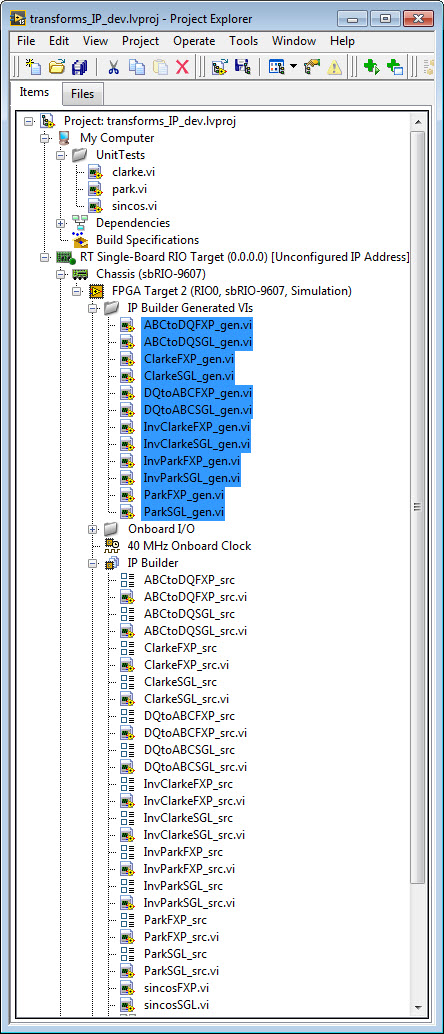

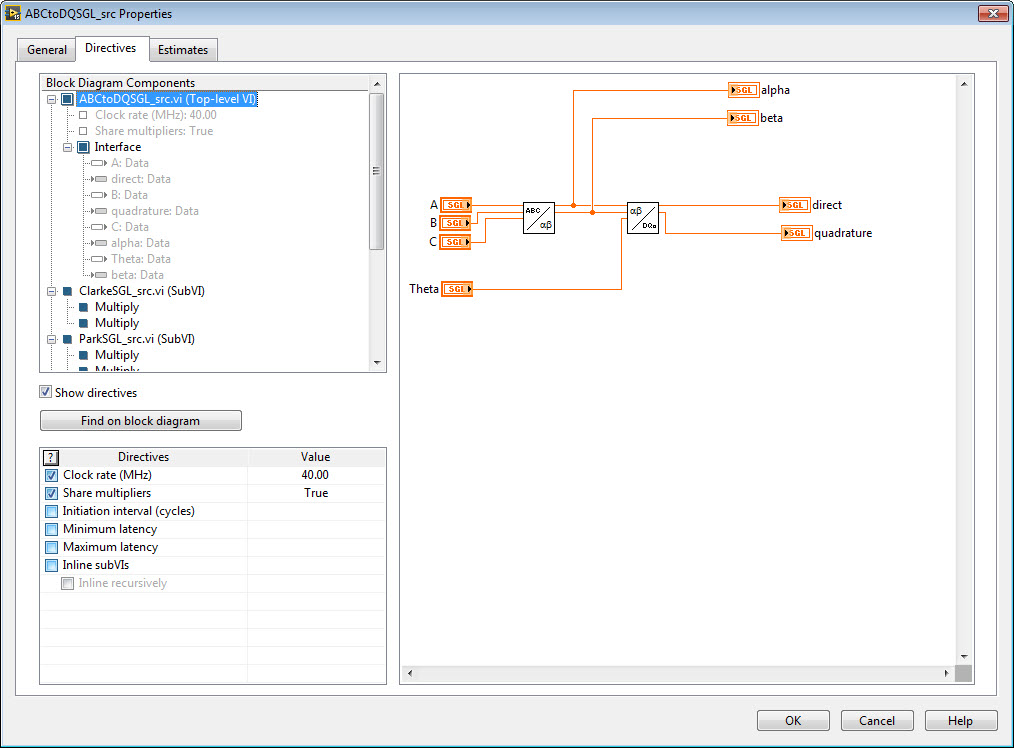

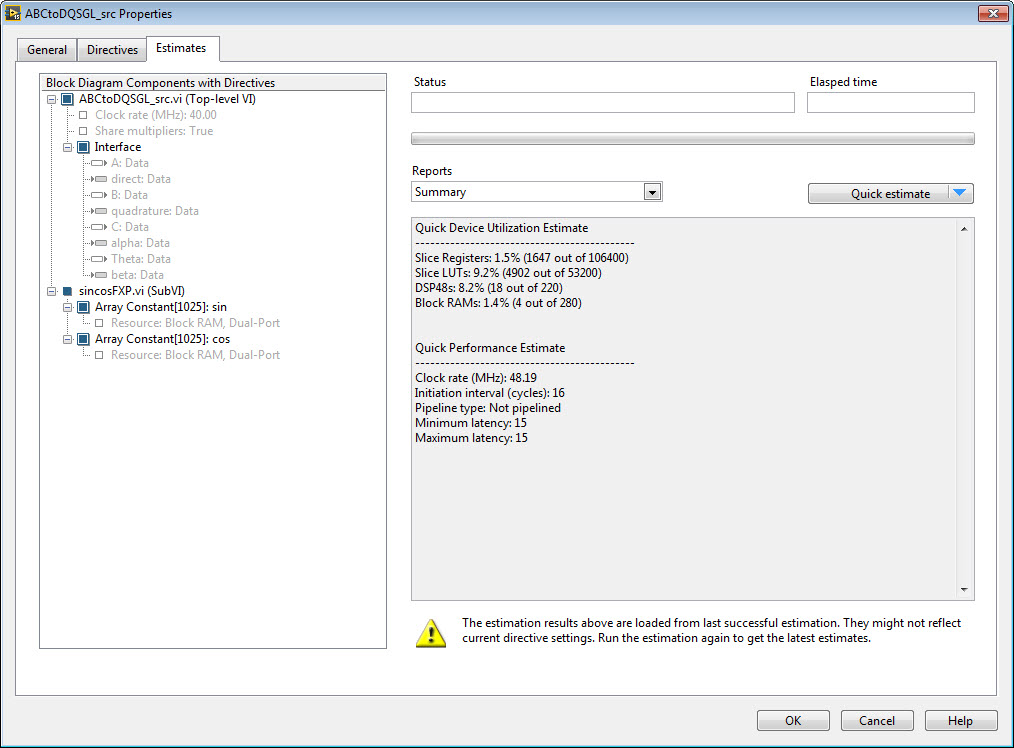

You can download resource efficient IP Builder versions of all of the most common transforms for power electronics here. Big thanks to NI systems engineer, Brian_K, for these!

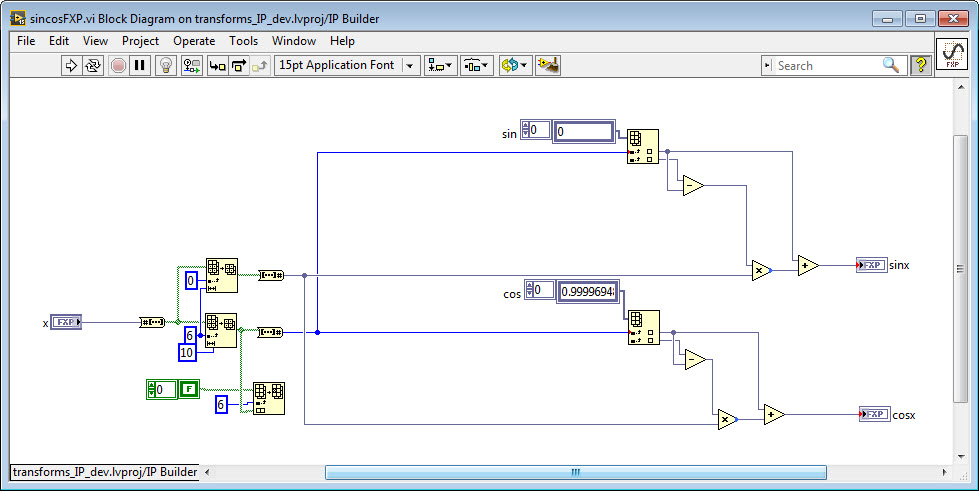

This free, open source library includes efficient floating point (and fixed point versions) of the following transforms:

Notes:

To learn how to use IP Builder to create highly resource optimized IP cores for LabVIEW FPGA, see this whitepaper. Please reply to this thread with any questions.

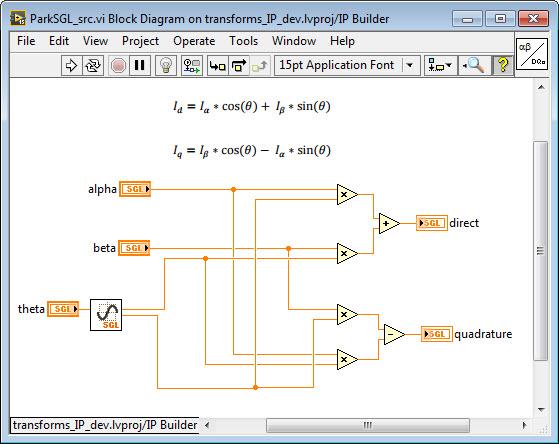

Here are screenshots:

10-27-2015 02:25 AM

Hi.

attached the tranformations I used with myRIO.

Avoid single or double arithmetic, I used FXP to save FPGA space. If you correctly size the FXP, rounding effects are negligible.

Cheers

10-27-2015 02:12 PM

Thank you for sharing these VI, one question is Im currently using 9606 in labview 2014. could you please give some details about how i can use this VI in labview 2014

Another question is I’m using the math script node on RT to do some matrix manipulation. I wonder is there a way that we can somehow generate a FPGA executable VI from the math script node ?

regards

jia

10-27-2015 02:12 PM

thank you

10-27-2015 03:07 PM

Hey

looks like you do your contorl on the RT level, which i have lots of problmes to do it.

In my control i have everything done in fpga level.

Initially, i want to only use the ADC and DIO on FPGA and get all the control done on RT level, however i have some many problem with the data transfer between RT and FPGA.

I still get it done on FPGA level(as the code attached https://drive.google.com/file/d/0B5gS1H0brOGgQW0wVFVTZ24wY0U/view?usp=sharing) However, if you can show me how you get the data transfer between RT and FPGA it will be great

Thank you

Regards

Jia

10-28-2015 03:19 AM

No, no,

high speed loops are closed on the FPGA, mainly in FXP: dq-axis current controllers for instance.

Data transfer between RT and FPGA is not so fast to allow you to close high bandwidth controllers on the RT target.

With respect to the FPGA model, this is one of the powerfull characteristics of LabVIEW: the source code is highly "uncorrelated" to the hardware where it will be executed. You mainly need to setup output pins...

"I wonder is there a way that we can somehow generate a FPGA executable VI from the math script node ?"

I really do not know, neverneeded this specific feature. You can do in the RT target: there are some specific blocks.

The VI I uploaded are designed to be used in the FPGA, put them in your FPGA VI: see help for more info.

Cheers,

AL3

10-28-2015 07:40 PM

thank you

now my main problem is i want to do a matrix inverse on FPGA level, i wonder if you know how to do that

thank you