From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

12-07-2015 06:28 AM

I am trying to design a 3-Ph Active Rectifier using the GPIC, and I'm interested in using floating point numbers this time.

I was able to modify availalbe AI scale loop for my application in SGL. Now the next step is to build a PLL. I am planning to start with a simple PLL by calculating atan2(-Vd,Vq) in stationary ref. frame.

Is there a atan2(Y,X) type function for SGL numbers in LabVIEW? Also are there any example codes in SGL for this kind of stuff?

12-07-2015 02:00 PM

You should check out the StarSim three phase thyristor bridge control example located here:

C:\Program Files (x86)\ModelingTech\StarSim\2.1\Examples\PowerSystem\Thyristor-Based HVDC.vi

See this thread for more info.

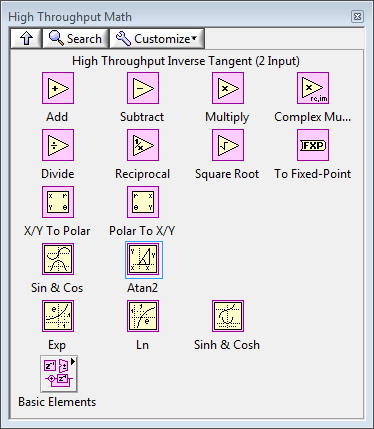

For arctangent, there is a high throughput math function on the palette (Programming>FPGA Math and Analysis>High Throughput Math>atan2). It returns the arctangent of y/x in pi radians, which use fewer FPGA resources than radians. To convert this value into radians, multiply by pi. Convert your floating point signals to fixed point at the inputs and outputs.

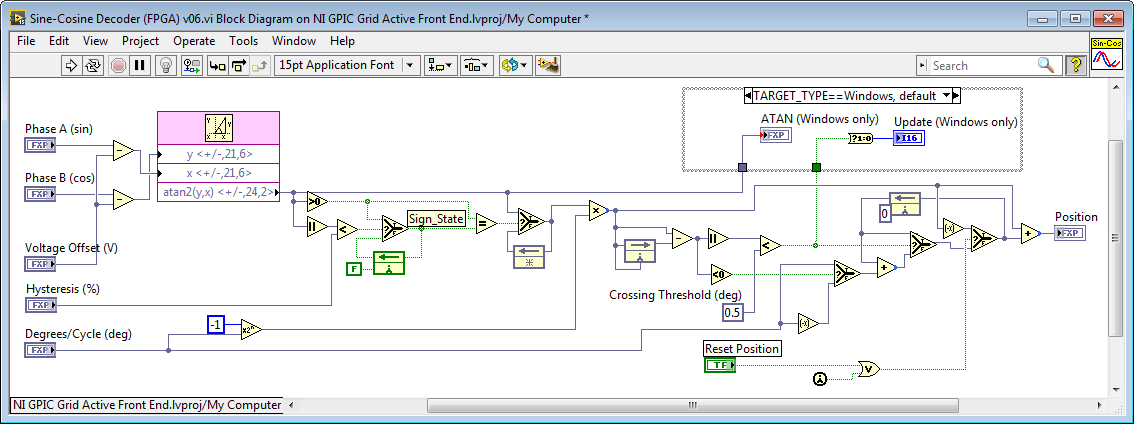

The discontinuity of the arctangent function can be problematic when the input signals have noise. The noise can cause the solution to jump back and forth if it happens near the boundary. Extra logic can be added to provide hysteresis and thereby make the atan calculation immune to noise. See the IP core below for an example, which was written for sine-cosine encoders. This is located in the power electronics control IP and examples library here: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Sun Tracking\Sine-Cosine Decoder (FPGA) v06.vi

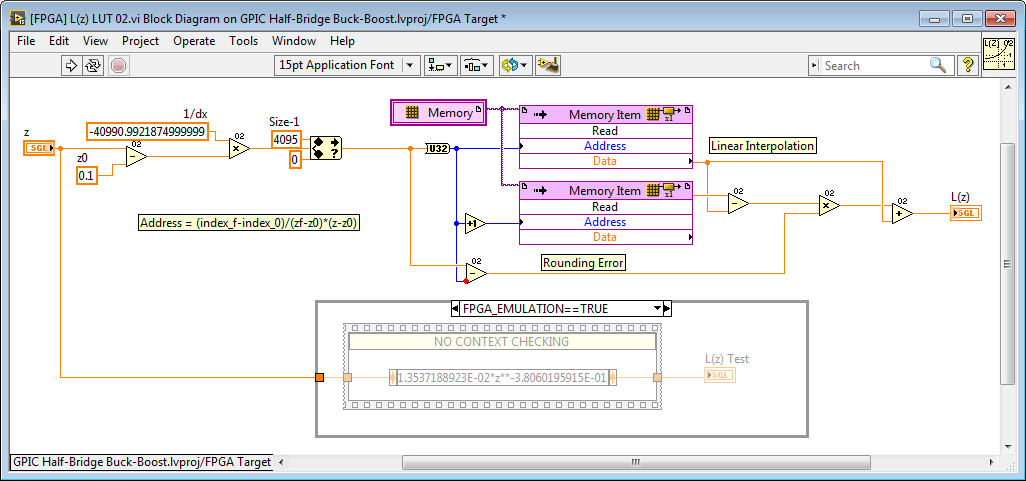

You could also implement the atan2 function as a floating point look up table with linear interpolation. See here for an example (non-linear magnetic inductance curve) that you could use as a starting point: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Polymorphic subVIs\Sine LUT 00.vi.

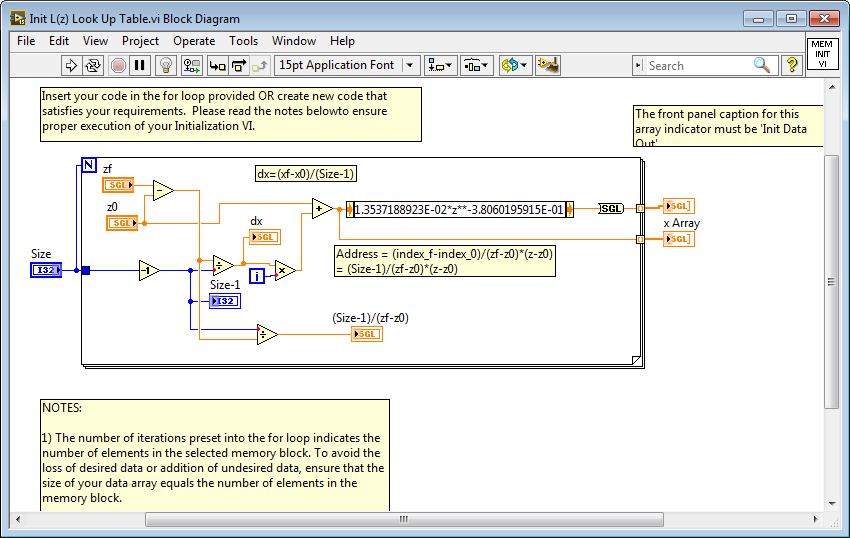

The initialization VI is setup to automatically calculate the necessary offsets when you change the look up table. The initialization VI is located here: C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\FPGA\[FPGA] L(z) LUT 02.vi. You would replace the L(z) formula node below with a floating point atan2 function. Note that this FPGA RAM initialization VI runs on the desktop. You'll need to copy the calculated value for 1/dx and Size-1 to the block diagram of your look up table with linear interpolation IP core.

There is a fixed point 3-phase PLL function included on the LabVIEW FPGA palette (FPGA Math & Analysis>Control>3-Phase PLL). To unlock the source code, right-click on it and select Open Front Panel. Note that the output theta is not in phase with Va, and a phase offset must be applied. See the following testbench for an example (C:\LabVIEW 2015\GPIC\GPIC Reference Design\Hands On Exercises\3-Phase Inverter\[Testbench] 3-Phase PLL Tutorial.vi).

There is a floating point 3-phase PLL function available with the purchase of StarSim for Windows or the StarSim Control Library. It is in the master library here: C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\IP Cores - LabVIEW FPGA\StarSim\[FPGA] StarSim_3PPLL_sub(lineV).vi.

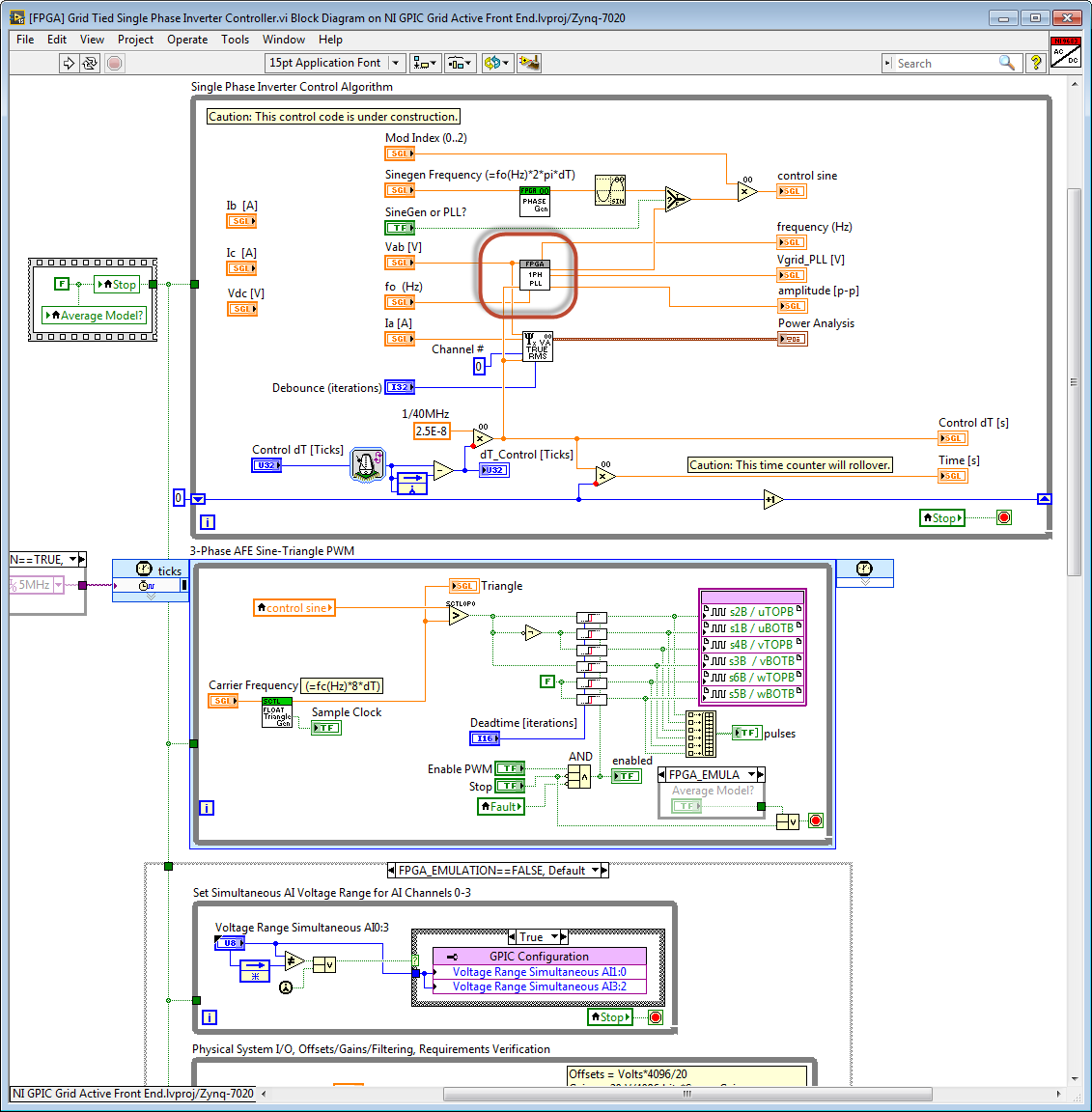

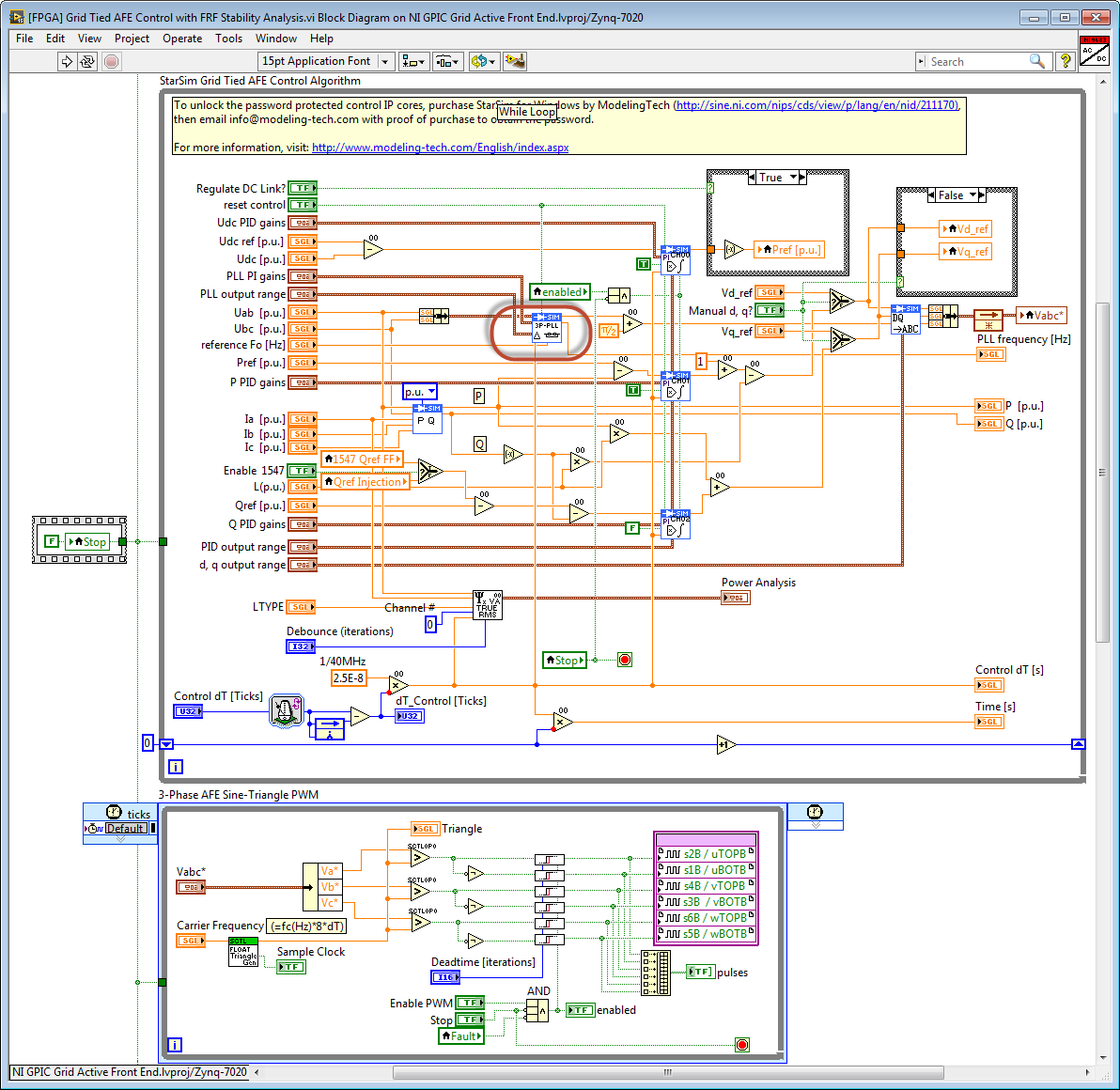

To unlock this password protected control IP core (circled below), purchase StarSim for Windows by ModelingTech (http://sine.ni.com/nips/cds/view/p/lang/en/nid/211170), then email info@modeling-tech.com with proof of purchase to obtain the password. For more information, visit: http://www.modeling-tech.com/English/index.aspx. Note that a phase offset is applied as shown in the screenshot below (C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Grid Tied AFE Control with FRF Stability Analysis.vi).

There is also an open source single-phase PLL in the power electronics control IP and examples library here: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] Single-Phase PLL with Frequency and Amplitude - Radians (FLOAT).vi. The output is in radians. The example below shows bipolar PWM-- it would be nice to update this example for unipolar PWM which provides twice the effective switching frequency. The example shown below is here: C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\SubVIs\[FPGA] Grid Tied Single Phase Inverter Controller.vi