- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Xilinx FIR Compiler 7.2 configuring issue

02-14-2018 05:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

I am currently working on an oscilloscopic board (8CH - PXIe-5170R) provided with FPGA Kintex 7. I would like to add a FIR filter to process the incoming data, channel by channel, and I tried to use the XIlinx FIR compiler 7.2, configured with a COE coffiecient vector created with Matlab. I didn't select any enable signal, so the IP should work with every sample. The problem is that this filter is continuously returning 0, so basically when my data pass through the filter they are completely eliminated (It is not a matter of cut frequency, because I chose a very high cut-off frequency and passed very low frequency signals). Any tips you can give on how to use this IP? Thank you everyone for your response

02-14-2018 06:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

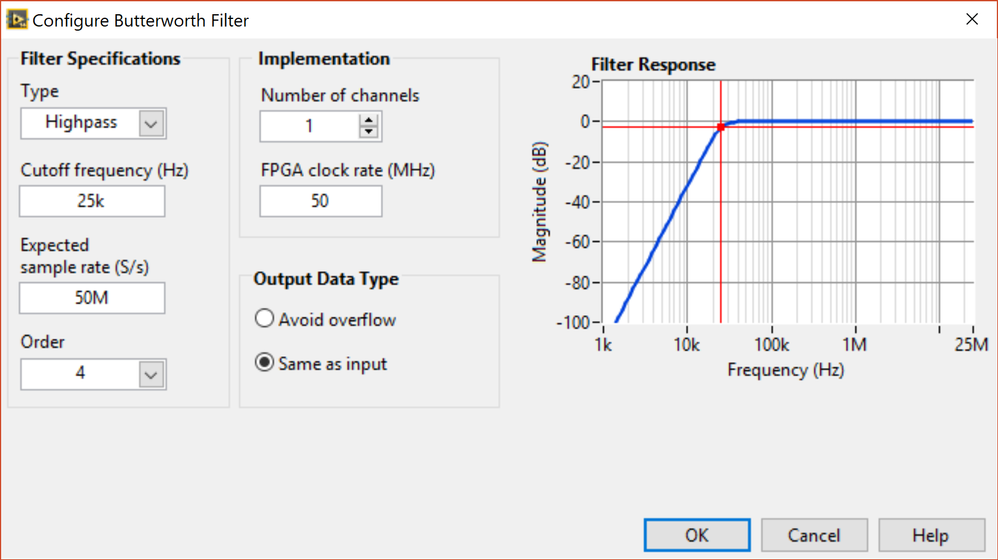

This is a tricky IP. Can you get by with the Butterworth Filter: http://zone.ni.com/reference/en-XX/help/371599L-01/lvfpga/fpga_butterworth_filter/ (if so, you will be finished sooner)

Moving right along:

Seems like you are using it in non-reconfigurable mode (i.e. no new coefficients after the FPGA is compiled).

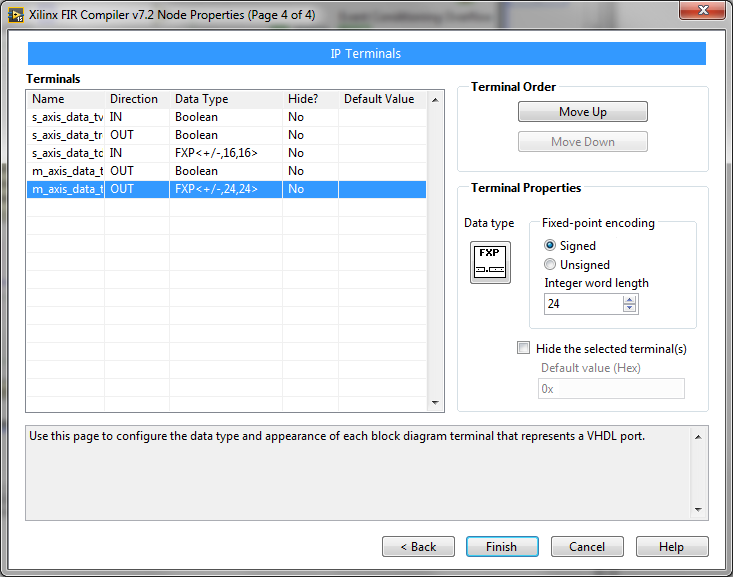

We have this working in both modes and here is a screenshot of the last part of the config which may offer some insights:

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-14-2018 08:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for the answer:

- unfortunately I cannot use the FPGA Butterworth Filter because I need to insert the processing in a single cycle timed loop, executing at data clock frequency, which is why I needed to use the Xilinx Compiler.

- I am using it in a non-reconfigurable mode. The problem is that my filter only returns 0. Besides, although I selected, in the initial configuration pages, "no enable signals", the vi results to be unexecutable unless I connect something to the "aclk" and "tdatavalid" pins. I tried to connect first a true constant, after a changing control "true - false - true - false - etc", but still the filter ouputs only 0.

02-14-2018 08:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Could you put the filter into another loop and FIFO the data over (so you can go with the Butterworth)?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-14-2018 08:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Since I am dealing with very high throughput applications (the incoming signal is processed with a digital deconvolution algorythm) I would prefer to avoid to FIFO data over, since this would bring me delays and timing issues...

02-24-2018 08:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

We are using the FIR Compiler on another project only because we need reconfigurable filter coefficients.

In another we do not have that requirement and have the Butterworth Filter Express VI running at 50 MHz. Do you need a higher rate?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

04-17-2018 02:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello crvmhl93

Did you found a sollution with the FIR Compiler 7.2 ?