Hello,

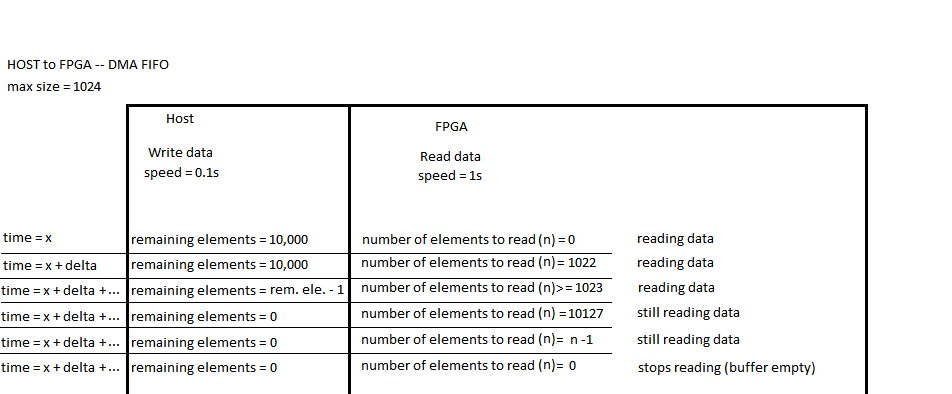

I am establishing a communcation from HOST to FPGA by using DMA-FIFO. Maximum size for this FIFO is 1024. Now from the host side, I am writing a data of 1-D array (Unsinged 64bit integer) into the fifo, and from FPGA side, this data is being read from the fifo. Now as i start the simluation, the default value of "Empty elements remaining" shows "10,000". further as the elements inside the fifo starts getting to read (at FPGA side), the "Number of elements to read" increases and when it reaches the value of 1024, then the "empty elements remaining" starts decreasing. The behaviour is described in the image (atteached).

while observing this behaviour of the FIFO, i discovered that this DMA FIFO, (having max. storage elements of 1024) also has an (additional) internal storage space of 10,000 elements. I might call it as internal buffer of this FIFO. now my question here is that, where are these (10,000 elements) values stored ?. as it is from HOST side, so is it the CPU storage ? or what ?

Thanks 🙂

Anum Sheraz