- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Is it possible to divide external sample clock frequency in PXI-5441?

11-10-2010 05:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I want to use external sample clock 10 MHz with PXI-5441 for generating arbitrary waveform with 1 MHz sampling rate. How can I do it?

Thank you.

11-11-2010 02:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Ventus,

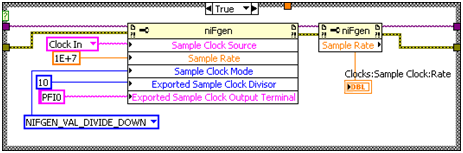

Yes you can do this. In order to do this in LabVIEW, use the property node called Sample Clock Timebase Rate and Sample Clock Timebase Source. I modified one of the example VIs and have a picture below for you to consult.

Jim St

National Instruments

RF Product Support Engineer

11-13-2010 01:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Jim,

Thank you for your answer.

I tried your example. It works, but it works with onboard clock anyway, although the niFgen.Sample Clock Timebase Source is “Clock In”. In other words in this example PXI-5441 generates waveforms without external clock.

11-15-2010 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Ventus,

How are you testing this to find that it uses the onboard clock? Did you not provide a clock on the Clock In and it worked anyways? If you could provide more information about this, I can look into this a little more.

Jim St

National Instruments

RF Product Support Engineer

11-16-2010 06:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Jim,

You are right. Really when I don't provide a clock on the Clock In it works. I believe it works properly if I set Clock In to Sample Clock Source and value of frequency (1000000) to Sample Rate.

11-17-2010 01:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Ventus,

I ran some tests on the PXI-5442 and I had the same results. I am going to see if R&D has any suggestions about it so we can figure this out.

Jim St

National Instruments

RF Product Support Engineer

11-18-2010 01:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Jim,

Thank you. I am waiting for your information.

11-18-2010 03:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Ventus,

I talked with R&D and here is what we found:

First, this property node can't be used with your card and after discussing this with R&D, this proprty node should be giving us an error when we even try to use it. I I have filed this as a bug under CAR: 258675.

Second, the reason why I thought this was possible was because of some confusing documentation in the FGEN Help. In the help it states under the device that the Clock In can accept an external Reference clock, external Sample clock, or external Sample clock timebase. This lead me to believe that this was possible but alas it isn't.

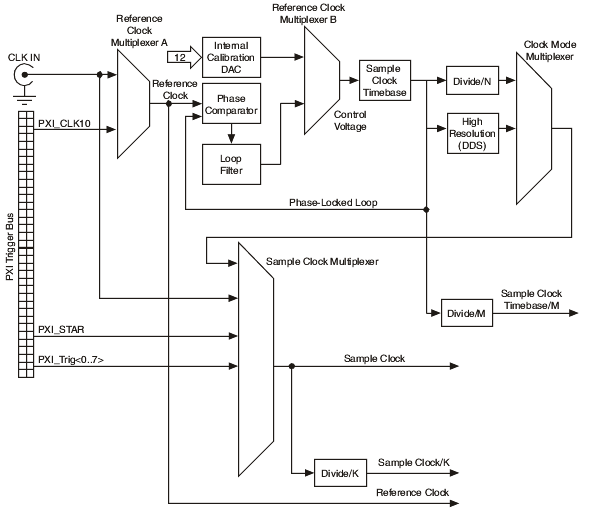

Knowing this, we do have some other tools to be available to us to get this down. In order to look into this, we need to consult the timing diagram for the 5441/5442. For this case we can look at either of them because the functionality is the same for Clock In. Here is the timing Diagram for the Help:

There are two things we can do. First we can PLL the the external 10MHz clock with the Sample Clock Timebase (top section of the timing diagram). Now that the device's timebase has been PLLed to your external 10MHz signal, we can create a 1 MHz signal from the timebase that will be in phase to your external signal. In order to do this, you can use the niFGEN Configure Clock VI to employ this.

The other way we can implement this is to use the Clock In as the Sample clock and use the divide down (Sample clock/K) to have it divide it down. In order to do this, we will have to set the Sample Clock Source, Rate, Sample Clock Mode (Divide Down), and the Exported Sample Clock Divisor (10 in this case). These property nodes can be found under Clocks >> Sample Clock.

Sorry for the confusion but this should straighten everything up.

Jim St

National Instruments

RF Product Support Engineer

11-22-2010 04:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Jim,

I haven’t done the first version you recommended so far. In the second version, Exported Sample Clock really is 1 MHz (I can see it if I export sample clock to PFI0 terminal). But the Sample Clock Rate isn’t changed (10 MHz).