- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA to FPGA Communication through PXI

Solved!09-17-2009 08:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Due to Input/Output constraints I need to find a way to send data between two different FPGA cards (specifically a 7852R and 7813R) on board a PXI-1042Q Chassis at a speed of approximately 1MSPS.

Does anyone know how this can be achieved/if it is possible (and if not there is a way to have 7 I/Os on one card).

Cheers, Ben

Solved! Go to Solution.

09-17-2009 08:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The short answer is yes. the technique uses a variation of SPI using the PXI data pins that are shared on both boards. to get the highest performance is kind of tricky.

I am a bit confused by your statement "and if not there is a way to have 7 I/Os on one card" what do you mean by this?

What is the data size of the sample that you are looking to transmit board to board?

09-17-2009 09:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Stu,

What we are trying to do is to implement digtial PDH locking for 8 cavities which means that all four input/output ports on one card (and all three on the other) will be needed. Otherwise we would only be using the one card. Currently, with only 2 cavities (and therefore no need for a second FPGA card) we are acheiving this by using a top loop running at 80 MHz and then using an indicator and a local variable of this indicator in the second loop (running slower ~1 MHz) to transfer the information.

For 8 cavities our idea is that one of cards will be running at 80 MHz collecting data and that every ~1MHz we would like to transfer a cluster containing 8 points (i.e. one for each cavity) to the 2nd FPGA (so not very big). Any help/advice you would be able to give on the subject would be greatly appreciated!

Ben

09-17-2009 09:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

by ports do you mean digital groups of 12 bits?

When you say you want 8 points, how many bits in each point?

what are you doing in your 80 MHz loop? digital I/O? I did not think you could run digital at 80 Mhz.

by using the PXI lines, you create a multi-line digital bus from master to slave. 1 clock, 1 sync. 4 data.

2 words per data line. clock rate up to 10 MHz.

On the other hand, NI showed FPGA to FPGA pipe using PCIe at NI-Week for very high bandwidth application.

this seems more down your alley. Not sure how far out this tech was from release but maybe NI can chime in.

09-17-2009 11:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

On one card we have 4x16bit high speed (80 MHz) digital inputs and the other has 2x16bit high speed digital and then 1 low speed (750 kHz) with 8 ips and 8 outputs. What I want to transfer is transfer a cluster of 8 values, all I64 once every ~80 ticks of an 80 MHz loop (i.e. every 1 MHz). In the 80 MHz loop we are taking the digital signal, demodulating it (i.e. timesing it by a sine wave generated in the loop) and then put it through a low pass CIC filter which decimates the signal by a factor of ~1/80 and it is this signal that I want to send from one FPGA to the other.

If it would make things easier I could attach a copy of the code if you'd like.

I don't suppose you had any example code showing how to do this?

Cheers.

09-18-2009 08:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If possible, could you post your project with code or email me directly. stu@viewpointusa.com

Thanks

Stu

09-21-2009 04:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello All,

You can certainly send information via the backplane for communication between R Series cards in a PXI chassis, however programming the communication protocol (SPI for instance) will be up to you to implement. In PXI R Series boards, there is a bunch of PXI I/O available to you. I would recommend using the PXI TRIG bus in order to facilitate communication between modules if you decide to go this route. For more on using signals on the PXI backplane, refer to How Do National Instruments PXI Boards Map to the PXI Backplane?

Sr Test Engineer

Medtronic, Inc.

09-21-2009 06:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

09-21-2009 09:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Chris_G. wrote:Hello All,

You can certainly send information via the backplane for communication between R Series cards in a PXI chassis, however programming the communication protocol (SPI for instance) will be up to you to implement. In PXI R Series boards, there is a bunch of PXI I/O available to you. I would recommend using the PXI TRIG bus in order to facilitate communication between modules if you decide to go this route. For more on using signals on the PXI backplane, refer to How Do National Instruments PXI Boards Map to the PXI Backplane?

Chris_G, in this link, it states that the 783xR can use the local bus. I have never seen how to do this. can you explain.

09-22-2009 01:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Stu,

The document is accurate. As far as R Series cards go, only the 781xR and 783xR can access the Local Bus lines, which do not include the lines that I mentioned in my previous post (PXI_TRIG lines). I did not recommend these because of the fact that Ben said in his first post that he is communicating between a 7813R and a 7852R. Although the 7813R can communicate on the Local Bus, the 7852R cannot, and therefore must use the PXI_TRIG lines if communication across the backplane is desired.

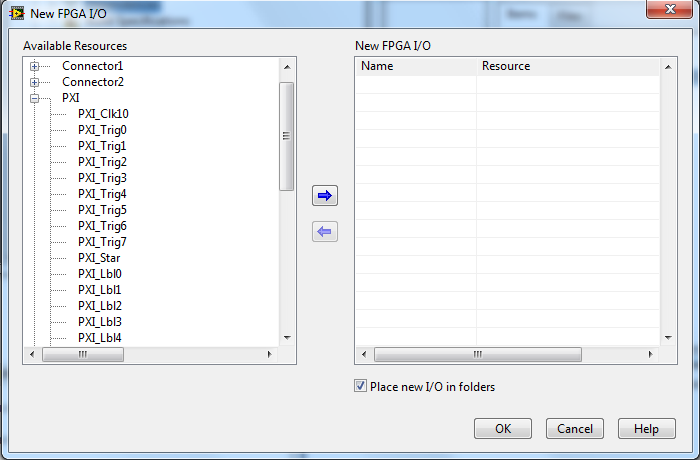

If you were to create a project with an existing or simulated 781xR or 783xR card, you will notice in the New FPGA I/O dialog that there is a PXI grouping, and underneath that you will see all available PXI lines to read/write. For these cards which have access to the Local Bus, you will not only see PXI_Clk10, PXI_Star, and all of the PXI_Trig lines, but also local bus lines, labeled PXI_Lbl0 – PXI_Lbl12 and PXILbr_0 – PXI_lbr12.

The Lbl and Lbr names stand for “local bus left” and “local bus right”. These buses are basically used to communicate information with adjacent slots to the left and right of the module. Once you have added the FPGA I/O to your project, you can drag & drop the corresponding I/O nodes into your project just like you would with any other FPGA I/O.

If you are interested in learning more, check out Accessing PXI Local Bus Lines Using R-Series Cards.

Sr Test Engineer

Medtronic, Inc.