From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

09-17-2018 03:39 PM

Hello Internet,

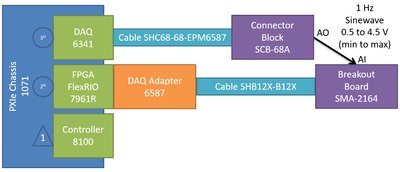

For a long period I have assumed I have not been able to read using the 6587 Serdes Channel due to a problem with my cable or read code, but I can read data using the Basic Connector fine and can confirm I and supplying a sinusoidal signal using a DAQ 6341 attached to the same PXIe chassis.

This setup was complicated as I was unsure how to set up the Acquisition Clock to get the Serdes Channel to run at a faster clock speed (I was helped by NI), but I still can not read anything from the FIFO but zeros. Does anyone have any suggestions? The end goal is to read a digital signal from a single channel at a rate of 1 GHz.

Best,

Ian

09-18-2018 03:51 PM

Hi,

Can you clarify what your set up is?

What are you trying to a digital signal on and where is this digital signal coming from?

Thanks,

Misbah

09-18-2018 04:25 PM

Hi Misbah,

This is my current setup. I have wired AO0 to IO1. The expectation is that it will read high voltages as a 1 and low voltages as a zero, thus acting as a discriminator so I can use it for pulse counting.

Does this setup make sense?

Best,

Ian

09-19-2018 03:56 PM

Hey Ian,

Some things to note about using this CLIP:

-When you reading from the SERDES Channel CLIP in your FPGA code, you read the last 10 bits acquired on the line all at once packed into a U16. The 10 bits with the data are 0-9, with 9 being acquired first

-There is an example for the SERDES Channel CLIP (NI 6587 Serial Acquisition - Configuration). This example acquires from a single LVDS channel. When you run this do you see the same results?

For reference: http://zone.ni.com/reference/en-XX/help/372614J-01/friohsdio/6587_serdeschan_clipref/

09-19-2018 07:32 PM

Hi Jon,

Thank you for the information on this CLIP. In response...

-I am aware of the packing. While troubleshooting I simplified my code to welcome any bit being 1, to ensure I was not missing data somewhere.

-I could not run the example in the example project (Error Code: -63192... project seems to expect a RIO device, while I am using a PXIe-1071 chassis). I had to move it to my project (attached earlier). After compilation and running from my project, I get the following error message (seen below) which I was getting before an NI rep helped me configure the acquisition clock in a complicated fashion I did not understand (seen in code attached earlier).

I really appreciate any help or guidance you can offer.

Best,

Ian

09-20-2018 11:06 AM

Hey Ian,

The only issue I see with your code is that Acq_Reset should be asserted after configuring the Acq clock source and then de-asserted after committing the settings(in the host code). I'd be surprised if this is causing the behavior you are seeing(all 0 data), however.

When running your code, do you see the counters you have returning correct values? If they are returning values which make sense with your clock rate then we can conclude that the loop is running and the clock is setup correctly.

If that's the case, what are you connecting to the LVDS channel +/- terminals?

09-26-2018 04:31 PM

Hi Jon,

I have been taking a long time because I have not been sure how to address your first point.

1) Not sure how to do this. Tried copying the part that Switches Write OFF/ON/OFF on the onboard clock to after the Commit flag is sent. Is that what you mean?

2) Double checking the number of FPGA Loops vs Real Time, I seem to be getting an FGA clock rate at about 1/5th of what I would expect. For 500MHz Clock Rate, I get 100MHz,and for 100MHz, I get 20MHz. Maximum I can get seems to be around 160MHz. This seems odd?

3) AI0+ (pin 68) from connector block SCB-68A (proxy for DAQ 6341) is connected to IO_1- on the breakout board. AI0- is connected to the cable shields and IO_1+. I have tried moving the input signal to other channels. On all IO_X+, the voltage seems to be railed between 0.75V and 1V.

Thank you for helping us.

Best,

Ian

09-27-2018 11:00 AM

Hey Ian,

1) I've attached a screenshot from one of the generation examples. After toggling the Xpoint Switch you need to assert either Gen_Reset or Acq_Reset after a new clock configuration is chosen to reset the clocking circuitry, then deassert to start the acquisition or generation.

2) The clock rate on the 6587 IO module is 500MHz, but the regional clock that your using in LabVIEW FPGA runs at a divided rate. This should match the serialization used to pass data to the SERDES. Looking at the continuous generation example, every Regional Clock cycle in LabVIEW FPGA (this is divided down IO clock) we pass 6 samples to the 6587 which it then clocks out one at a time (IO clock is running 6x faster than Regional Clock).

3) For the actual data, be sure your giving a signal within the LVDS input specifications provided in the manual. There is a table on page 4 which shows the max/min differential and absolute voltages:

http://www.ni.com/pdf/manuals/375614c.pdf

If you believe that everything is configured correctly but are still seeing strange behavior, or to have an in depth conversation with one of our Applications Engineers about the device, I would suggest opening a support request. We'll be able to look into the behavior you're seeing in more depth on an official support ticket.