- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

help Veristand 2016 matlab model

06-16-2017 09:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello friends,

my working environment : Matlab 2015b32bit + Veristand 2016 in Window7.

after under the guide:

Problem:

The Windows SDK 7.1 installs the compiler required to create models for Windows and PharLap ETS VeriStand systems. However, setting up the SDK on a Windows 8.1 or 10 machine is prone to failure. What is the recommend installation method for this SDK on Windows 8.1 and Windows 10?

Solution:

The following method has been used to successfully install the SDK 7.1 on both Windows 8.1 and Windows 10:

- Uninstall all Microsoft Visual C++ 2010 Redistributable packages (both x86 and x64) via Control Panel � Programs and Features.

- Install the Windows SDK 7.1. During installation, under the Installation Options menu, uncheck Visual C++ Compilers and Microsoft Visual C++ 2010.

- After the installation, apply the Microsoft Visual C++ 2010 Service Pack 1 Compiler Update for the Windows SDK 7.1 patch.

- Reinstall the Microsoft Visual C++ 2010 Redistributable packages: x64 and x86.

With the compiler installed successfully, you are ready to compile models for both Windows and PharLap ETS targets.

then, in matlab model can be successfully:

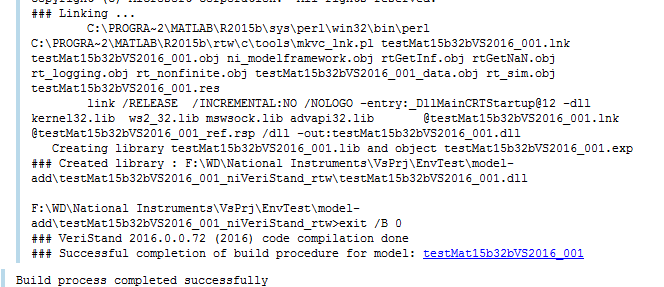

### VeriStand 2016.0.0.72 (2016) code compilation done

### Successful completion of build procedure for model

but the .dll cannot run correctly in Veristand 2016 project. no calculation was executed in VS window or RT machine.

Can anyone help, thanks in advance.

06-21-2017 02:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi wisejohn, I heard a similar problem with Matlab and VeriStand.

Which hardware drive do you install Matlab and VeriStand?

This is the thread in Japanese.

06-28-2017 08:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Win10,even PC simulation fail!

06-29-2017 10:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello John,

Would you please clarify on what doesn't work?

- Does the model successfully load in System Explorer or does it return an error stating of an incompatibility?

- Or the model loads in System Explorer, but at execution the model's returned data is unexpected.

Have you tested the behavior of a simple and minimal model design? For example, would you please verify that a single multiplication in the model properly executes when stepped in VeriStand.

07-01-2017 03:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks,see details followed:

MATLAB2015B 32bit,

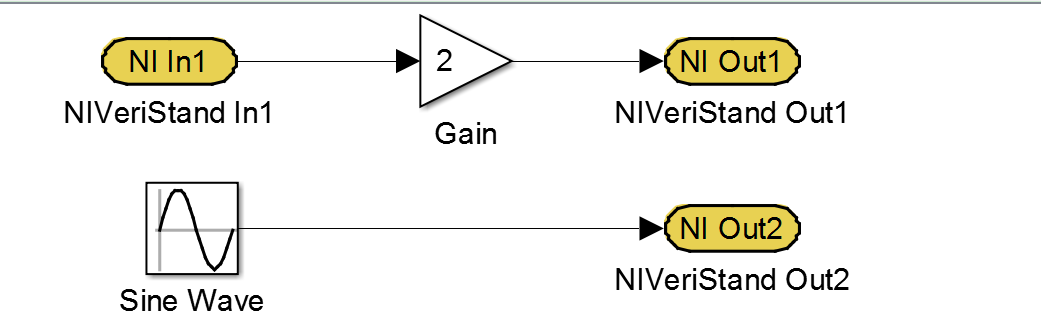

Model:

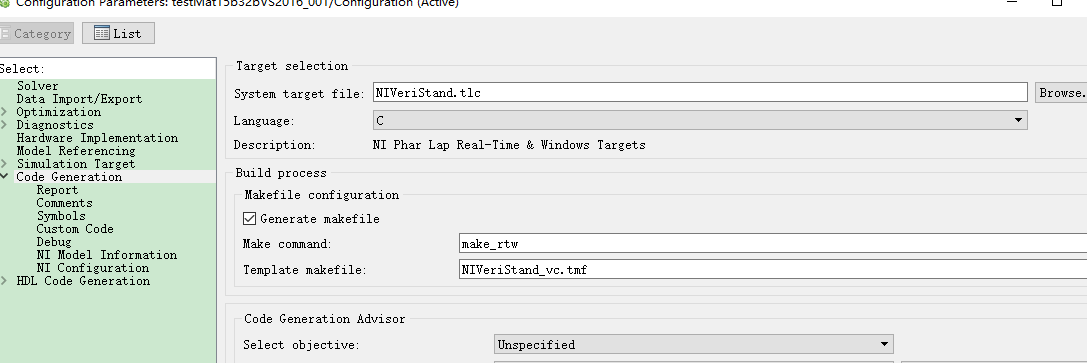

config setting:

Build:

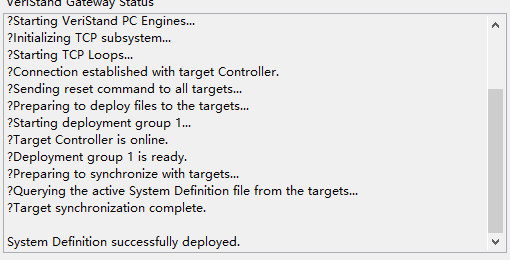

VS2016 project and Deployed

runing(no data sine wave or did not work!!!)

07-01-2017 03:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

NestorG 已写:

Hello John,

Would you please clarify on what doesn't work?

- Does the model successfully load in System Explorer or does it return an error stating of an incompatibility?

- Or the model loads in System Explorer, but at execution the model's returned data is unexpected.

Have you tested the behavior of a simple and minimal model design? For example, would you please verify that a single multiplication in the model properly executes when stepped in VeriStand.

Thanks,see details followed:

MATLAB2015B 32bit,

Model:

config setting:

Build:

VS2016 project and Deployed

runing(no data sine wave or did not work!!!)

07-04-2017 02:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi John,

Try, please, using regular Matlab In/Out ports. I have some models compiled with Matlab 2016a for Veristand 2016 and they work like a charm.

Hardware Engineer @ ZF

07-04-2017 02:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Regular Matlab In/Outports should work. They must be in top level model.

CLA, CTA, CLED

07-04-2017 10:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You may use an indicator to check the model state.

07-05-2017 05:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello John,

This is actually a known issue. We fail to export ports if the model only references VeriStand Port blocks. To resolve the issue you must have at least one Simulink Port in the model design.

The only reason to use a VeriStand Port block is if you desire to access the port within a subsystem; otherwise, I encourage you to use Simulink's Port blocks. The Simulink Port blocks offers greater support for various data types than a VeriStand block.

Note that the issue is fixed with the release of VeriStand 2017.