- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT FIFO Custom Device Details

Solved!04-25-2013 02:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I've got a couple questions on the VeriStand FIFOs in an asyncrounous custom device.

I saw a post a while ago about tying a -1 to the RT FIFO Read function to allow it to wait indefinitely for an element to enter the FIFO. This helps pseudo-synchronize the PCL with an asyncrounous custom device. I am wondering if this causes the custom device thread to sleep or does it stay active and keep polling? Is there a way to change from polling to blocking?

Another quick question, if I only want to write to the RT FIFO when data has changed will this cause any unforeseen issues? Like the channels timing out or need to wake up or anything? Under certain conditions may only write to the channels once every 1000 iterations of the PCL and custom device loop.

I know that I cannot write to selected channels within an RT FIFO, but could I create multiple FIFOs within a custom device to effectively do the same thing? I imagine then having outputs 1, outputs 2 etc within VeriStand.

Thanks,

B

Solved! Go to Solution.

04-26-2013 03:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi B,

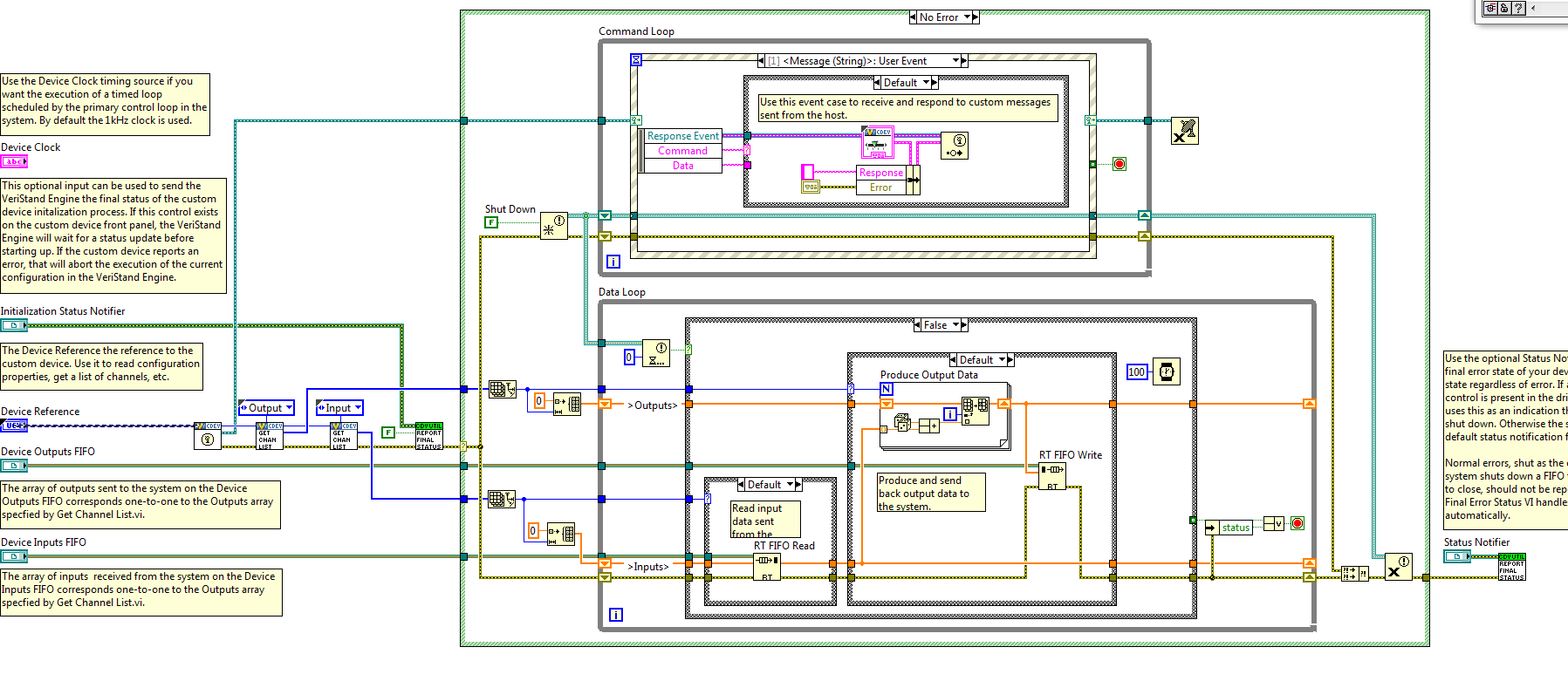

If you look at the RT driver VI generated from the custom device template you will see exactly what's going on. If you set the timeout for the FIFO Read to -1 then the botton loop will be essentially paused unless there are elements to read in the FIFO. During this time the thread will be still active because the RT read VI is polling data for the amount of time specified in the timeout. I don't think there is a way to change the FIFO mode to blocking since the FIFO reference is passed on from the Veristand engine to the RT driver VI.

The PCL writes and reads data to and from asynchronous custom device FIFOs at each execution step. In your custom device you can configure it to just read and process the data from 1000th step. I don't see any issues with it.

You can only have one FIFO for input channels and one FIFO for output channels. You can write to a given output channel by writing data to an element at given index in the output array that is being passed to the RT FIFO Write function.

Senior Systems R&D Engineer | Wireless | CLA

National Instruments

04-26-2013 05:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

if in your configuration code you use the VI "set loop type" and set timed loop and use timing source true .. Then in your rt driver code you can time a timed loop from the timing source string provided. That will cause the timed loop to wake up only when new data is written to the fifo.

you can also use the set decimation VI to control how often veristand writes to the fifo.