From 04:00 PM CDT – 08:00 PM CDT (09:00 PM UTC – 01:00 AM UTC) Tuesday, April 16, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From 04:00 PM CDT – 08:00 PM CDT (09:00 PM UTC – 01:00 AM UTC) Tuesday, April 16, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

10-22-2012 05:56 PM

Hey,

I've been looking at the use of the PXI_Trig lines, and I was wondering if I could get help with a few questions.

From documentation, I understand about the risk of hardware damage if a PXI_Trig line is double-driven

by two or more devices. I know that I need to reserve trigger lines, using either MAX or programmatic control,

and that I need to configure propagation over multi-segmented buses.

However, I also want to dynamically configure my FlexRIO boards through register writes so that one board, acting as master, generates a

signal that is received by other FlexRIO boards on a common PXI_Trig line. Essentially, a case structure in a SCTL tied to a register would determine whether a board is driving or receiving on that PXI_Trig line. Obviously, the system would be set up so that only one FlexRIO's config register would be set to the "master" value at any one time. Is it possible to configure the PXI_Trig I/O resource as input or output dynamically like this, and if so is it safe to do so?

In any event, is the LabVIEW FPGA module adding synchronization registers "under the hood," so to speak, for this I/O resource to guard against metastability?

If so, how many registers?

Lastly, could anyone suggest a good way to implement a VHDL-style if/elsif/elsif/else priority encoding structure? I imagine a case structure (maybe nested) and a boolean array wired into the case from all the triggering sources might do it, but I thought that all that nesting might be resource inefficient on FPGA, and wondered

if anybody had done it a different way.

Once again, I'd be grateful for any suggestions.

10-23-2012 09:53 AM

However, I also want to dynamically configure my FlexRIO boards through register writes so that one board, acting as master, generates a

signal that is received by other FlexRIO boards on a common PXI_Trig line. Essentially, a case structure in a SCTL tied to a register would determine whether a board is driving or receiving on that PXI_Trig line. Obviously, the system would be set up so that only one FlexRIO's config register would be set to the "master" value at any one time. Is it possible to configure the PXI_Trig I/O resource as input or output dynamically like this, and if so is it safe to do so?

In the FlexRIO Development Tools, there is a Broadcast on FPGA IO VI (in the FIDL»Helper VIs palette) that utilizes the Set Output Data and Set Output Enable methods to implement a bidirectional I/O line. A boolean configures whether output is enabled, that would be your master? input. Here's a screenshot:

In any event, is the LabVIEW FPGA module adding synchronization registers "under the hood," so to speak, for this I/O resource to guard against metastability?

If so, how many registers?

You can check pretty easily in the LabVIEW project, right-click the I/O item (PXI_Trig0, for example) and select properties. Look in the Advanced Code Generation category:

By default, it looks like these lines get 1 Sync Register for Output and Automatic (typically 2) for the Read.

Lastly, could anyone suggest a good way to implement a VHDL-style if/elsif/elsif/else priority encoding structure? I imagine a case structure (maybe nested) and a boolean array wired into the case from all the triggering sources might do it, but I thought that all that nesting might be resource inefficient on FPGA, and wondered

if anybody had done it a different way.

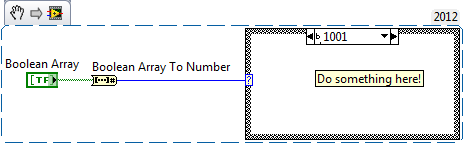

I personally don't like nesting a case structure more than once, so if you have a deeply-nested loop you'd like to implement, you can encode the boolean array into an integer and then use a single case structure:

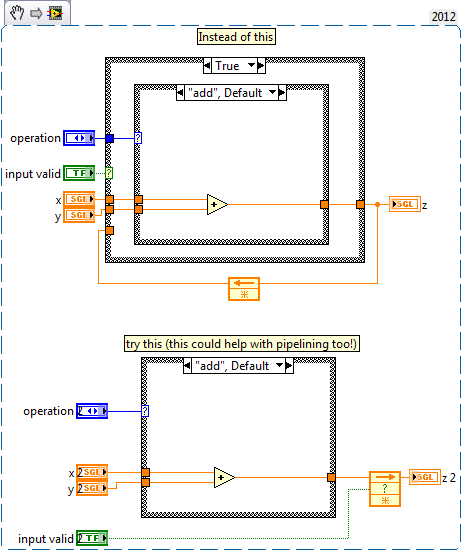

Also, depending on your VHDL implementation, it may make sense to use boolean functions on your outputs instead (or a feedback node with the enable terminal included):

The above is a pretty simplified example, but hopefully gives you some ideas.

10-26-2012 02:46 PM

Thanks for the help.