- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Compile Error with PXIe-5785 (KU060) Timing Violation at GTHE3-CHANNEL_X1Y12

12-26-2020 10:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, I am trying to generate waveform from two DRAM banks to two AO channels on PXIe-5785.

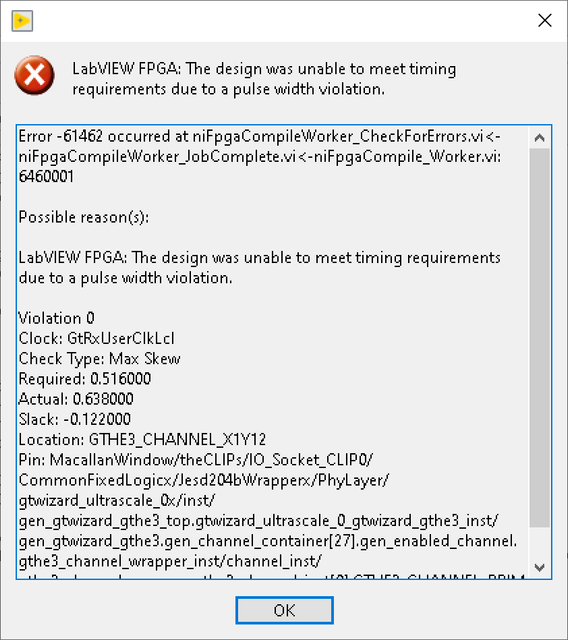

Then, following compile error occurs.

Above error is generated as Xilinx Error, and not like ordinary timing violation error of LabVIEW FPGA. Therefore, it is hard to tell what part of my FPGA code generates this error.

Would anyone tell what this timing error indicates, and how to work around this timing error?

Best regards,

12-27-2020 07:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When I see these kinds of errors, I roll back to code that did compile. Did your code ever compile?

The shipping example could be a place to start. Can you post your code here?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

12-28-2020 12:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the comment. Though I am still interested in any debugging guidelines for FlexRIO with such specific error messages, the error message indicates occurrence of timing error at non-diagram component. Timing error of non-diagram component is usually listed in regular timing error window, latest series of FlexRIO with UltraScale may generate non-diagram component errors which are related to its IO on different window through XIlinx Error button.

Below is what I did to debug and got compilations success at this moment.

- Compilation Failed : 3.2GSps AO stream from 2 DRAM banks on PXIe-5785 with my own generation engine

- Compilation Succeeded: same as 1 above, but with Implicit Enable remove

Let me provide an additional information as a member of FlexRIO Network Community, I tested Waveform Generation Engine IDL with PXIe-5785 with some slight modifications with WFMGEN IDL.

WFMGEN IDL cannot catch up with AO stream in the following case.

- 1.6GSps AO stream with 1 DRAM banks (267MHz DRAM clock, 200MHz Retrieval, 256bit provide per DRAM and U32 x8 consumption at retrieval)

- 3.2GSps AO stream with 2 DRAM banks (240MHz Clock for DRAM, 200MHz Retrieval, 512bit provide per DRAM and U32 x16 consumption at retrieval)

(*1 After waveform is loaded on host-side, write grant time is set smallest and read grant time is set largest, priming depth is set largest)

(*2 For the case 2 above, WFMGEN IDL does not natively support x2 DRAM banks, but WFM Storage does, so I modified Create Resource of WFMGEN. This does not meet 267MHz timing but does 240MHz. )

This may be due to very flexible waveform sequencing of WFMGEN IDL which results in a bit tricky DRAM access pattern.

Then, found 1.6GSps AO stream with 2 DRAM banks (240MHz Clock for DRAM, 200MHz Retrieval, 512bit provide per DRAM and U32 x8 consumption at retrieval) can work without underflow error.

Thanks!