- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PXIe-6259 Maximum Clock Reference of 10 MHz

07-12-2010 02:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I'm currently using a PXIe-6259 to generate Digital Output.

According to the specs of this DAQ card:

"DO Sample Clock Frequency:

Regenerate from FIFO: 0-10MHz

Streaming from Memory: 0-10MHz"

I've used one of the shipping example (Write Dig Chan-Ext Clk.vi) to test the maximum limit of the DAQ card in generating Digital Output.

The two clock sources that I've tried:

1. 100kHzTimeBase

2. 10MHzRefClock

When using 100kHzTimeBase (10us per tick) as the clock source, there is no problem in the generated output.

However, when using 10MHzRefClock (100ns per tick), these are the problems I faced:

1. -200016 error (Onboard device memory underflow)

- even when I set the Sampling Rate to 10M S/s, Number of samples to 10M samples.

2. I used an oscilloscope to capture the screenshot of the digital output:

- instead of seeing a 1second of digital pattern, there is about 200us long of digital pattern (This probably because of the memory underflow problem)

- The 200 us long of "digital pattern" is actually triangle waveform instead of square waveform.

I wonder what is the problem here? Could someone please advise what do I need to do to know if the DAQ card can generate Digital Output at 10MHz Reference Clock?

Thanks.

howmean

07-12-2010 05:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I think I might have misunderstood the specification. Could someone please correct me if I'm wrong?

"DO Sample Clock Frequency:

Regenerate from FIFO: 0-10MHz

Streaming from Memory: 0-10MHz"

Previously I thought Sample Clock Frequency refers to the reference clock source to be selected, but this Sample Clock Frequency actually refers to the "Number of Samples per second (S/s)". Did I interpret wrongly again?

"I wonder what is the problem here? Could someone please advise what do I need to do to know if the DAQ card can generate Digital Output at 10MHz Reference Clock?"

I should rephrase the question which I've posted previously to: "How can I generate Digital Output at 10MHz clock frequency without error?"

I tried with the following configuration using "Write Dig Chan-Ext Clk.vi" (shipping example):

1. Physical Channel: /port0/line0

2. Clock Source: 20MHzTimebase, 80MHzTimebase

3. Sample Clock Rate: 10 M S/s

4. Number of Samples: 1 M, 10 M

I didn't see "-200016 Memory Underflow problem" now, but I always get "-200716 error" which says:

"Measurements: Digital output detected a new sample clock edge before the previous sample could be written from the onboard memory.

If you are using an external sample clock, ensure that it is connected, within jitter and voltage level specifications, and without glitches. If applicable, reduce your sample clock rate or use a product capable of higher sample clock rates."

howmean

07-12-2010 12:21 PM - edited 07-12-2010 12:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi howmean,

The DO Sample Clock Frequency refers to the maximum update rate of the DO. That is, the maximum rate that you may update the DO waveform. Generating a waveform like {1 0 1 0 1 0 ... } may result in something that looks more like a triangle wave depending on what you have it connected to.

The problem that you're seeing now is that you are setting the sample clock to be the 20MHz or 80 MHz timebase. The Sample Clock Rate is just used by DAQmx as the expected rate of the clock to determine buffering and such, but this input does not actually change the frequency of the timebase. If you want to use the 10 MHz Reference Clock for your sample clock, you'll have to select it as the timing source (e.g. /Dev1/10MHzRefClock).

The -200716 error is what you would expect if your clock is way too fast (e.g. 20 or 80 MHz). The -200016 error is what you would see if not enough data is getting to the board quickly enough. Some questions to consider:

- Do you have other modules on the bus?

- What chassis/controller are you using?

- Could you try the shipping example using the 10 MHz Reference Clock for your sample clock instead of the 20 and 80 MHz timebases?

Best Regards,

07-12-2010 10:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi John,

Thanks for your quick reply.

The PXI chassis that we are using is PXIe-1065. I'm just using Port0/Line0 to generate Digital Output.

I've tried with 10MHz Reference Clock by choosing "/PXI1Slot7/10MHzRefClock" as the Clock Source in the shipping example.

the rest of the settings:

Sample Clock Rate: 10 M S/s

Number of Samples: 1 M

I get "-200016 Memory Underflow" error.

The thing which I don't really understand here is:

- for AO generation, the default clock source used by 6259 is the 20MHzTimebase, and yet I do not see "-200716" error even when generating at the 2.86 MS/s (maximum sampling rate for single channel AO)

- so what is the difference here between AO and DO?

Please pardon my lack of knowledge in using DAQ.

Another question is:

I select "100kHzTimebase" as the clock source with the following settings:

Sample Clock Rate: 1MS/s

Number of samples: 100 K

Normally for AO, with the above Sample Clock Rate and Number of Samples setting (no regeneration), I would expect to see a waveform with a duration of 100 ms.

However for DO, I saw digital pattern with a duration of 1 second (it follows the 100kHz timebase).

Again, would like to ask, why is there a different behaviour between AO and DO?

howmean

07-13-2010 12:11 PM - edited 07-13-2010 12:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Howmean,

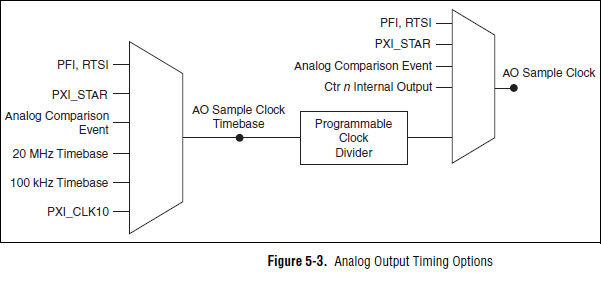

I think you're confusing the sample clock and the timebase. By default, the AO Sample Clock is derived from the 20 MHz timebase. However, the default sample clock is not the 20 MHz timebase, but rather a divide-down of it. From the M Series User Manual:

-200716 is an error specific to DO tasks, are you sure this is the error you are receiving on your AO task? Nonetheless, you should not set the 20 MHz timebase to be your sample clock source for your AO task (it will use Counter 0 to perform the routing, but the driver does let you make this route). Rather, just leave the timing source unwired and choose the desired rate to use the divided-down 20 MHz timebase.

The DI and DO subsystems don't have their own timing engines, so the clock must come from somewhere else (the Device Routes tab in MAX will show you all of the options). One of these options is the 10 MHz Reference Clock. The Sample Rate input to DAQmx Timing only directly affects the sample rate if you are using the internal timing engine (remember, this doesn't exist for DI or DO tasks on an M Series). If using an "external" source, then the Sample Rate input to DAQmx Timing.vi does not actually change the rate (but does help determine things such as default buffer size).

Having said this, I am still a bit surprised that you are not able to achieve10 MHz on the PXIe-6259 for your DO task. One thing to keep in mind is that the PXIe 6259 is actually native PCI, and uses a PCI to PCIe bridge to fit the PXIe form-factor. Perhaps the issue is just getting the initial data to your board to provide an adequate buffer for the generation.

Since the 10 MHz reference clock is always present, as soon as the task starts it will begin clocking out samples. My guess is that we need to delay the clock source a bit to allow time to fill the onboard FIFO of the device before starting the generation. This isn't possible if using the Reference Clock as your timing source--I would try using the internal Frequency Generator which can be started and stopped as needed. The attached code shows what I have in mind.

Best Regards,

07-14-2010 03:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi John,

Thank you once again for your support and clear elaborations.

I got a better idea now.

I tried the example which you've attached above.

One of the subVi in the example (Create Digital Waveform.vi) was created in LabVIEW 2009, so I replaced that subVI with the one in Write Dig Chan-Ext Clk.vi.

The maximum Sample Clock Rate that I can go up to is 2.5 MHz.

I'm still getting the "-200016 Memory Underflow" error when trying to generate at 10 MHz Sample Clock Rate.

Despite the error, I could see a digital waveform of about 400 us on the oscilloscope.

I'll get in touch with NI local support to find out if there is any problem with the hardware (hopefully not).

Keep you updated on this.

Thanks,

howmean