- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

High frequency digital inputs to FPGA cannot be detected correct

Solved!01-21-2013 12:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

We want to connect the CMOS camera to PCIe-7842R with SCB68 box to analyze image in FPGA. There are PCLK (pixel clock) signal (36 MHz) and 8-bit data.

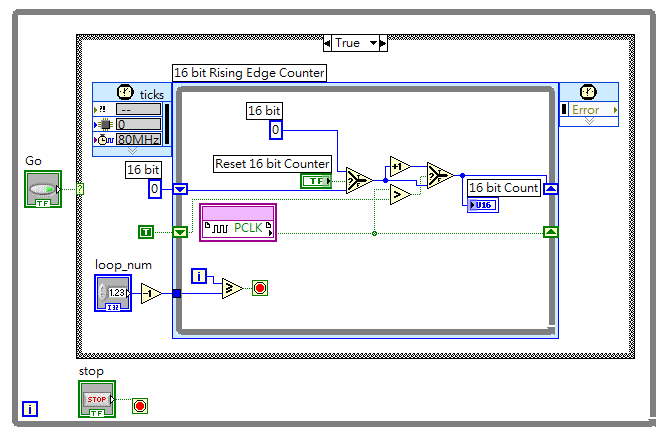

At 1st, we write a test program to make sure that we can detect the PCLK correct which is attached as program.png. The program is very simple that there is a timed-loop with 80 MHz which should be sufficient to catch 36 MHz signal. If "Numeric 2" set to 8000, we should have 3600(+ -1) as "Numeric." The reason why we have (+ -1) is because of that we don't have any sync, so it is acceptable in this test program. And we can get the right result in this setup.

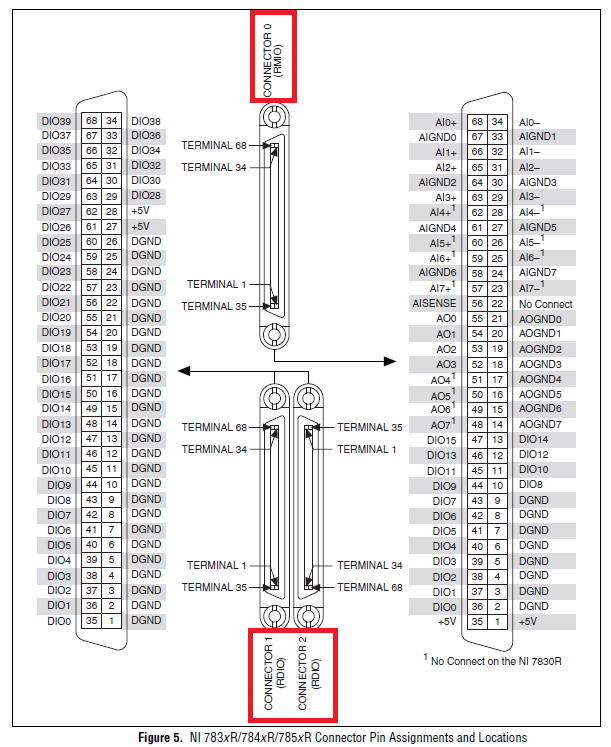

2nd part, we plug the 8-bit data into FPGA and we get the wrong result of PCLK. Even we only plug 1 bit (which is labeled as DIO1 in program) data, the PCLK is disturbed and we can't find why. The connector setup is attached as connector.jpg.

We have tried to make the 2 digital signals far apart but still fail. We have tried to change the cables connected between SCB68 and FPGA from SHC68-68-RDIO to SHC68-68-RMIO cable because we think it may have a better shielding. We have a better result but still wrong.

Now, we set "Numeric 2" to 8000 and we have around 3400~3500 as "Numeric." which is wrong.

Does anyone have any advice or command about this problem? I will very appreciate your kind help.

Thanks.

Solved! Go to Solution.

01-22-2013 01:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

For your first question, I suggest you to run the LabVIEW shipping example to make sure there's nothing going wrong in your coding.

Yor can refer to the folliowing example to implement a custom rising edge counter.

Modify it to fit your application.

Try to test your result with this code.

For your second question, I think there might be cabling and termination issue.

Please refer to the following two pages to check if you have done proper terminations.

http://digital.ni.com/public.nsf/allkb/72579EBFD781E95E862572AD0001FEDD

http://www.ni.com/white-paper/3854/en

BR

01-22-2013 08:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Thanks for your response. I have also read the articles about the impendance match when we are in MHz range. The result is correct when I input CPLK alone. If I have 2 signal inputs (CPLK and 1-bit data), I will get wrong result.

The code I have modified is as following:

PCLK is 36 MHz. It means if I input 8000 to "loop_num" and I will get 3600 (+ -1) from "16 bit Count" with 80 MHz clock. The strange part is that If I only input PCLK alone, I will have the right result. If I have 2 signal inputs (CPLK and 1-bit data) simultaneously, I will get wrong.

I also tried to change the cable from SHC68-68-RDIO to SHC68-68-RMIO and I have a better result. I am wondering that if there is any suitable cable that I can use for MHz signals.

I will continue trying to test the impendance between FPGA and camera. If I have any result, I will note here. If anyone has any comment, please give me some advices.

Thanks.

01-22-2013 07:26 PM - edited 01-22-2013 07:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

According to your description, it looks like the crosstalk indeed affects the testing result.

Can you do cross verification between CPLK and 1-bit data, which means test them individually?

See if the result fits your expectation.

When it comes to cable, I think the only difference between RMIO and the RDIO is the analog part.

http://digital.ni.com/public.nsf/allkb/2873867ECCF3790B862573B40059ED2A

RMIO fits for both analog and digital signal while RDIO fits only for digital.

It depends on which IO you select then the cable shouldn't be changed.

Check the following image to better understand what I mean.

If you connect the RMIO cable to the RDIO connector, you will get the wrong measurment, vice versa.

Thank you

Ting

01-23-2013 12:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks Ting,

I checked the cables. I used to think the AI in MIO cable should have a better shielding, so I expect to have a better result in my test. The result is wrong in both cases.

I try another setup to test the impendance. I input the 1-bit signal to a 50 ohm resistor in bread board. And I have the correct result of PLCK signal counting.

Now, I am wondering what is the impendance about the FPGA digital input. It should be also 50 ohm, right? Maybe there is someting impendance mismatch between FPGA, cable and SCB68 box.

Thanks.

01-23-2013 11:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ccmkn,

Check the following link. It mentioned that the DI is high impedance and doesn't require a latch to hold the data.

http://digital.ni.com/public.nsf/allkb/25E58AC9D7E9450386256DDD000D93B3

Furthermore, according to the spec, it indicates the input impedances are as follows.

Thanks

Ting

01-24-2013 01:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ting,

Thanks for your patient replay and discussion.

I found the document listed the input impedance that you said.

http://sine.ni.com/ds/app/doc/p/id/ds-98/lang/en

I think the 10G ohm is for analog input, not for digital inputs. According to the architecture of the DIO, it should also be high impendance. The signals from camera is with 50 ohm output impedance, and cant match the input impedance of FPGA. In this manner, if w are in MHz application, we can't just use the cable and SCB68. Am I right, or I still miss something?

Thanks.

01-29-2013 09:43 AM - edited 01-29-2013 09:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ccmkn,

I escalated your question to the AE in the US and got some conclusions.

First of all, it's a pity that you won't (necessarily) get the signal integrity you need on your R Series card unless the DIO is running lower than the 1-5MHz range.

The reason for this is the native clock for R series is 40 MHz.

The minimum pulse width of the digital input signal is 25ns. For a signal to have a minimum pulse width of 25ns, its period must be 50ns or longer, meaning that its max frequency is 20MHz. In that sense it should be possible to acquire at 20MHz, but in practice it requires significant signal conditioning design and effort on their part.

Even if you can derive the sample clock up to 200 MHz, the signal conditioning circuit still needs to be acomplished to solve the problem.

However, it doen't seems to be easy to finish this task since you have to build your own circuit.

In conclution, R series should be able to acquire at 5MHz with quality signal conditioning, and that if you wants faster you should get an HSDIO card (if you don't need FPGA), or a FlexRIO card (if you do need FPGA).

Thank you

Ting

NITW AE

- Tags:

- R Series bandwidth

03-18-2013 08:13 AM - edited 03-18-2013 08:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ting

Because of your answer,I try to find the difference between PCIe-7842R and FlexRIO. But I can't find the difference between them.Their FPGA both are Virtex-5.

Why FlexRIO can be faster?

Please help me

Thanks

03-18-2013 08:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator