- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

rt - unable to deploy model and fpga code

02-24-2015 06:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi all,

we are having trouble getting our code to deploy to a rt target and fpga

We are unable to use the network shared variables to communicate between the FPGA and RT target, details below, does anyone have a suggestion?

system:

Host : windows 7, NI Labview 2014, MIT / Vertistand installed

Target: PC with Labview RT & PCIe 7852R FPGA

we have a standalone working FPGA code working (verified) and we added a "Network Published Shared Variable with RT FIFO enable using Single Element"

our idea is to read an encoder and calculate the counts (this part works) using the FPGA, we then want to send that info to a vi running on RT target and display the value. eventually our RT target will have a model/controller built , but right now we only want to read and display a single value.

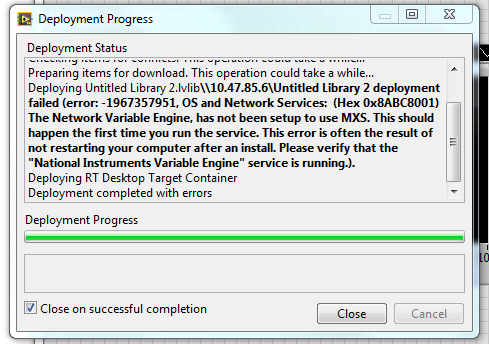

When we run, we get the following erros:

based on reading the forum, we tried to reset the MAX database to get the "NI Variable engine" because the windows services shows the ni variable engine is not running.... we tried this and it did not work...

any help will be apprecated,

also here is our project structure...

02-26-2015 10:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi JK,

Are you sure you're trying to use network published shared variables to communicate between the FPGA and the RT target? Could you explain that a bit more or provide code screenshots (or actual code)? Typically, there are two ways to communicate with an FPGA VI: read/write controls, and a DMA FIFO (the thrid, less common way, is User-Defined I/O Variables). These methods are abstracted when using VeriStand because the XML you import (the *.fpgaconfig file) tells VeriStand how to interact with the bitfile via these methods. If you are using the Model Interface toolkit, you are using LabVIEW (not VeriStand), so you will need to get the encoder values from the FPGA via read/write controls or a DMA FIFO. This is accomplished on the RT side by using the FPGA interface functions palette:

FPGA Interface VIs and Functions

http://zone.ni.com/reference/en-XX/help/371599K-01/lvfpgahost/fpga_interface_palette/

Transferring Data between the FPGA and Host (FPGA Module)

http://zone.ni.com/reference/en-XX/help/371599K-01/lvfpgaconcepts/fpga_data_transfer_overview/

The RT code can read and write to network published shared variables, but the FPGA cannot access them.