- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

pxie 7841R waiting on falling edge - electrical signal get dirty

11-15-2021 04:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi All,

I am reading a square wave which high and low levels are 5 - 0.3 Volt.

On the oscilloscope I can see a good square wave until I connect the FPGA 7841R Digital input.

If the FPGA is connected the signal is apparently still good but sometimes appear spurious falling edges.

I know that the FPGA properly work, generating a square wave it can read the falling edges and if I set the FPGA to read on rising edge it calculates properly (but rising edge are not good in the system).

My tests were:

- add a pull down resistor (2 kOhm) to discharge parasitic capacity and it had quite no effect

- add a series diode and parallel resistor (2 kOhm) to remove the 0.3 Volt and it deteriorates the falling edge

My question:

How can I read that signal more accurately, without spurious falling edge?

Is the problem in the 0.3 Volt of the low level also if the FPGA threshold for low level is 0.8 Volt?

Thanks in advance

03-25-2022 10:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well, no one has replied however the problem is still there.

I overcome the problem by insertion of a coaxial cable between my device output and the FPGA NI 7841r digital input.

I don't know how long the cable is, probably more than 50 meters.

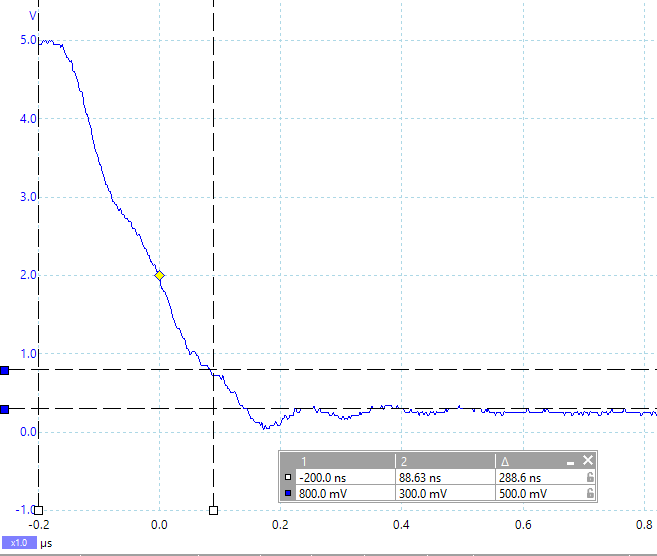

I also took two screen of the oscilloscope focused on the falling edge of the signal with the FPGA connected here

and without the FPGA here

I would like to remove the cable and use a more clever way to solve the problem, but I cannot find the more clever solution.

I hope that someone suggest something to try.

Thanks

03-25-2022 10:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You've not said anything about the frequency of the signal. I would recommend adding a 50 ohms series resistor if the signal is above 5MHz, this will avoid any reflections.

Soliton Technologies

New to the forum? Please read community guidelines and how to ask smart questions

Only two ways to appreciate someone who spent their free time to reply/answer your question - give them Kudos or mark their reply as the answer/solution.

Finding it hard to source NI hardware? Try NI Trading Post

03-25-2022 03:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Youre right, the frequency isn't a problem it's just a 1500 Hz square wave, the problem is visible when the duty cycle vary from 50 %.

In my opinion it could related with the high frequency harmonic.

Otherwise the generator, which give the output by a pull up resistance, doesn't allow the discharge of the FPGA input.