- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ni 9234 fifo dma dropping samples

Solved!02-24-2014 01:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I've got an issue when sampling using the cRIO and an AI card NI 9234, Currently configured to sample a 1k Hz signal from signal generator on FPGA side going directly to DMA which is (1023 elements in size) to the host side (1 million element size). Using producer, consumer architecture and saving to tdms on the consumer side. The producer has the read from dma fifo. Please see images any help would be great ! ![]()

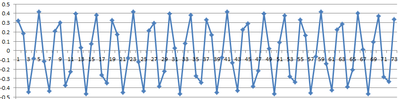

If i plot the data i get this :

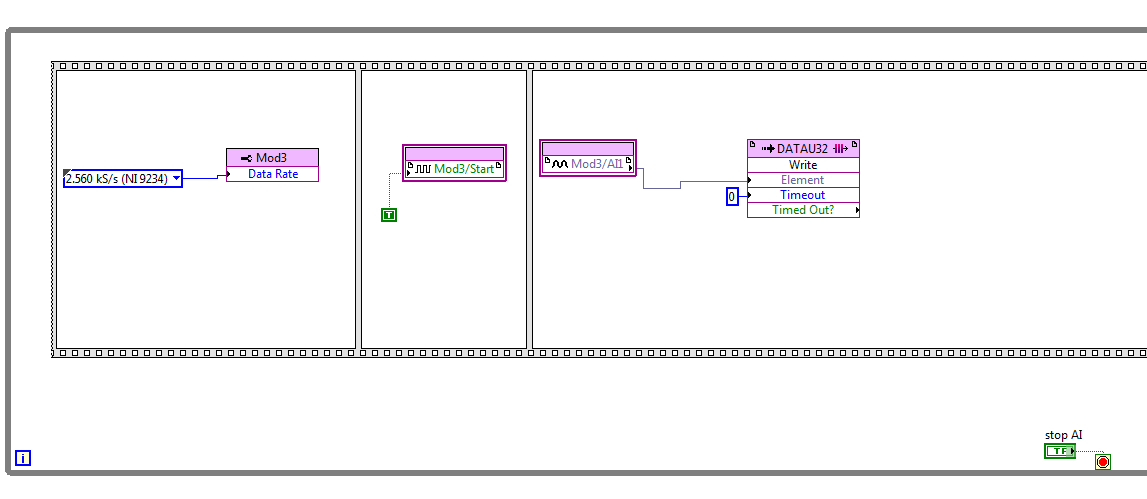

Here is my FPGA code :

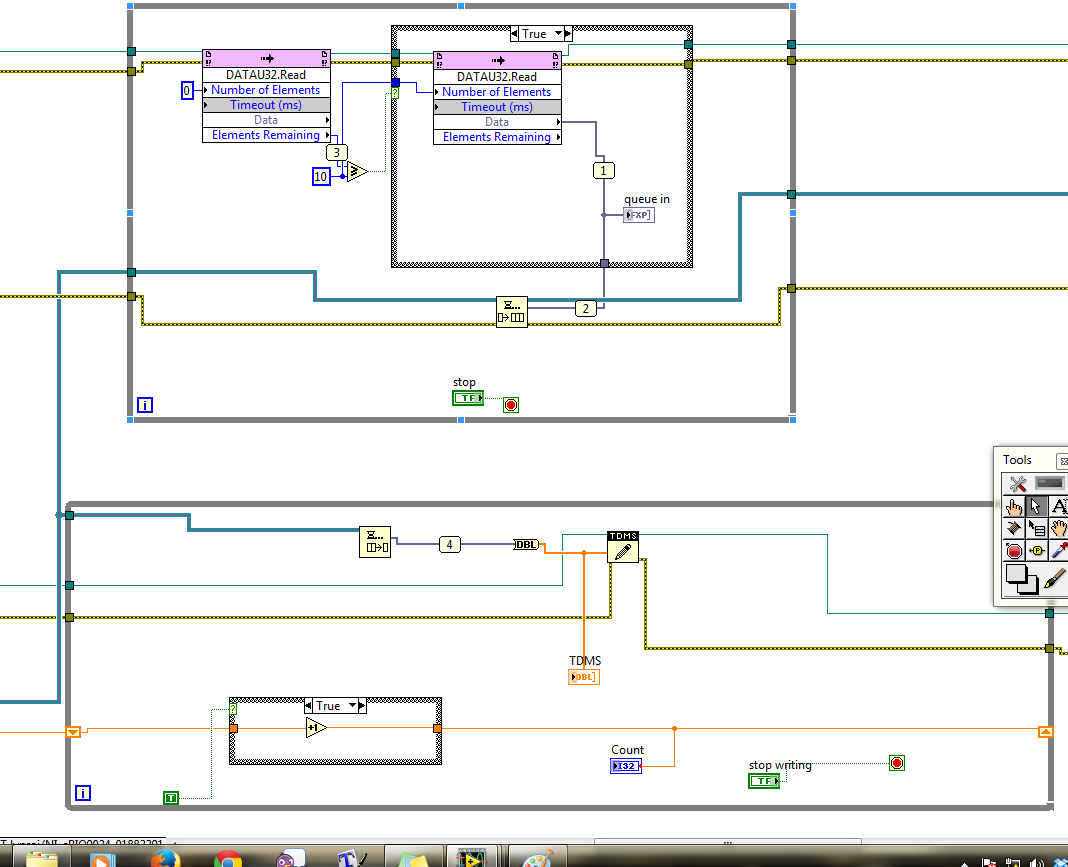

Here is my host side :

Solved! Go to Solution.

02-25-2014 06:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi leapingfrog,

To get the shape information of a signal, you need to generally sample at a rate of 5-10times the frequency of the signal. In your case since the signal frequency is 1kHz, you need to sample at a rate of 5-10 kHz (the higher the better). You can change the data rate of the module to a higher value (maybe 10.240ks/sec) and check if this makes things better.

Thanks and Regards,

Supreeth.K

02-25-2014 06:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I tried sampling at higher rates, basically i tried all the available settings all the way up to 51.2k s/s and i still get a graph like i've posted. The only difference i notice is when i drop the input signal to 10hz, then it works. Anything above that i get the same problem. I thought it could be with a specific setting. I change the sampling rate then simply save the vl file and rebuild the project deploying to the cRIO.

Do you have any other suggestions as i'm kind of stuck ![]()

02-25-2014 10:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator